# THE UNIVERSITY OF HULL

# Public Key Cryptosystems

-Theory Application and Implementation

being a Thesis submitted for the degree

Doctor of Philosophy

• in the University of Hull

by

# Anthony Joseph McAuley, BSc

April 1985

To my Mother and Father,

who given the same opportunity...

### SUMMARY

Summary of Thesis submitted for PhD degree

by Anthony Joseph McAuley

on

# Public Key Cryptosystems

The determination of an individual's right to privacy is mainly a nontechnical matter, but the pragmatics of providing it is the central concern of the cryptographer. This thesis has sought answers to some of the outstanding issues in cryptography. In particalar, some of the theoretical, application and implementation problems associated with a Public Key Cryptosystem (PKC).

The Trapdoor Knapsack (TK) PKC is capable of fast throughput, but suffers from serious disadvantages. In chapter two a more general approach to the TK-PKC is described, showing how the public key size can be significantly reduced. To overcome the security limitations a new trapdoor was described in chapter three. It is based on transformations between the radix and residue number systems.

Chapter four considers how cryptography can best be applied to multi-addressed packets of information. We show how security or communication network structure can be used to advantage, then proposing a new broadcast cryptosystem, which is more generally applicable.

Copyright is traditionally used to protect the publisher

-1-

### SUMMARY

from the pirate. Chapter five shows how to protect information when in easily copyable digital format.

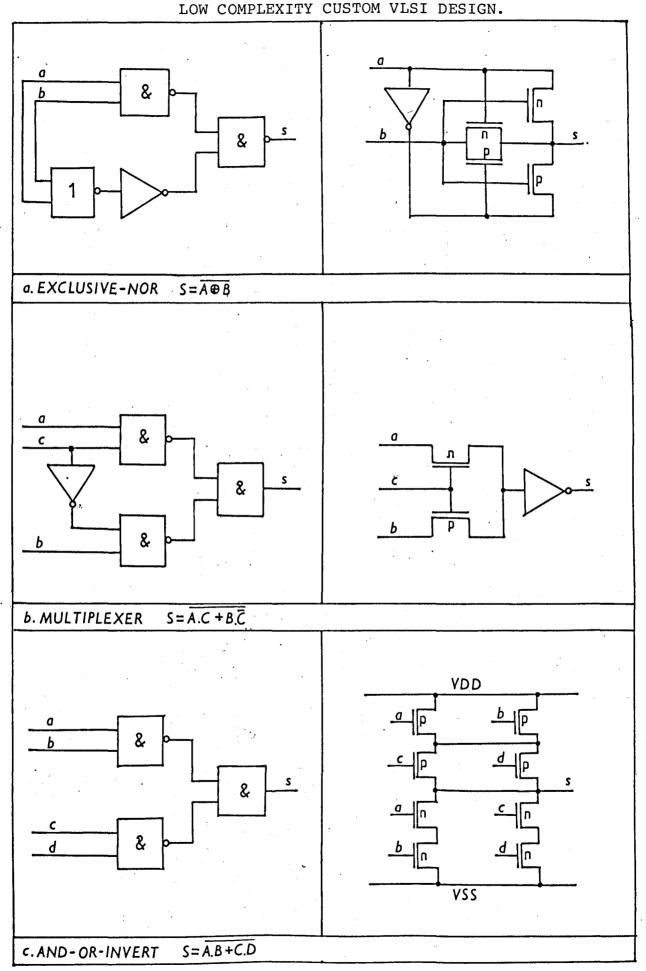

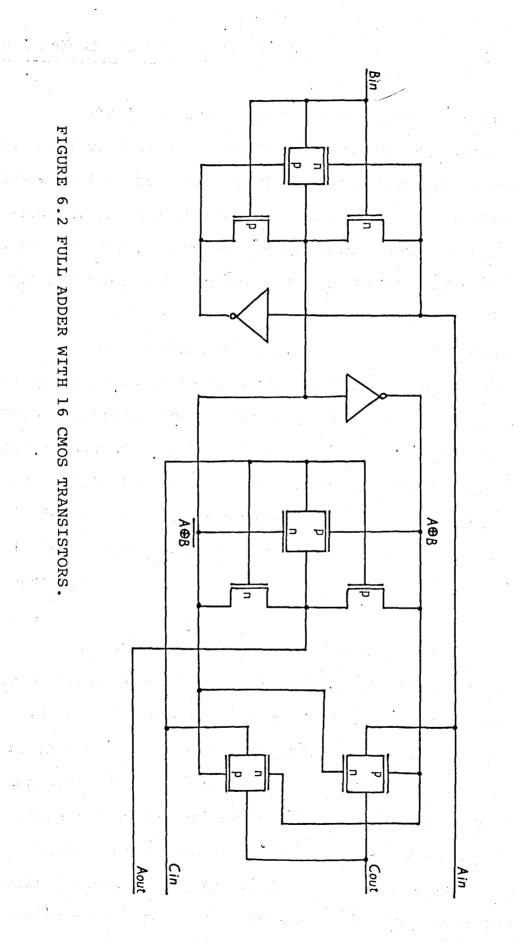

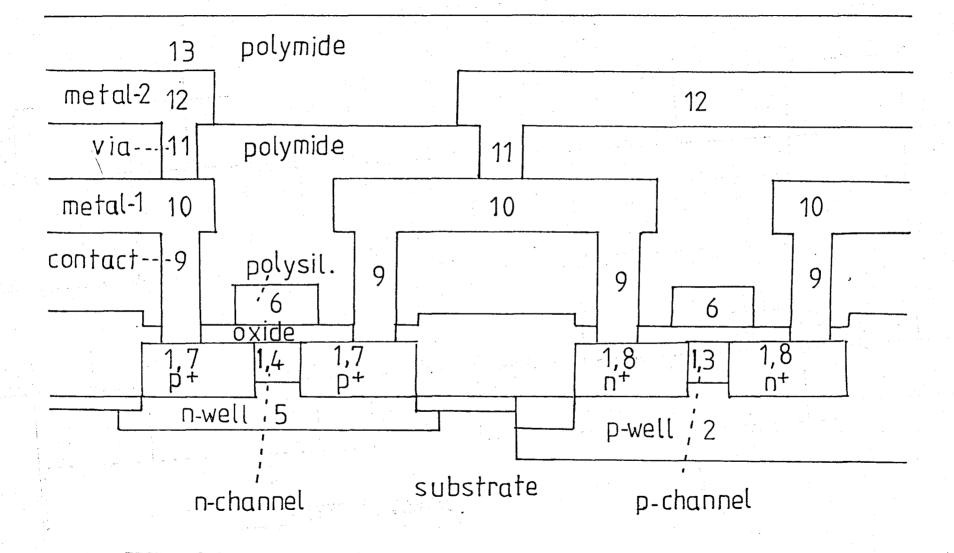

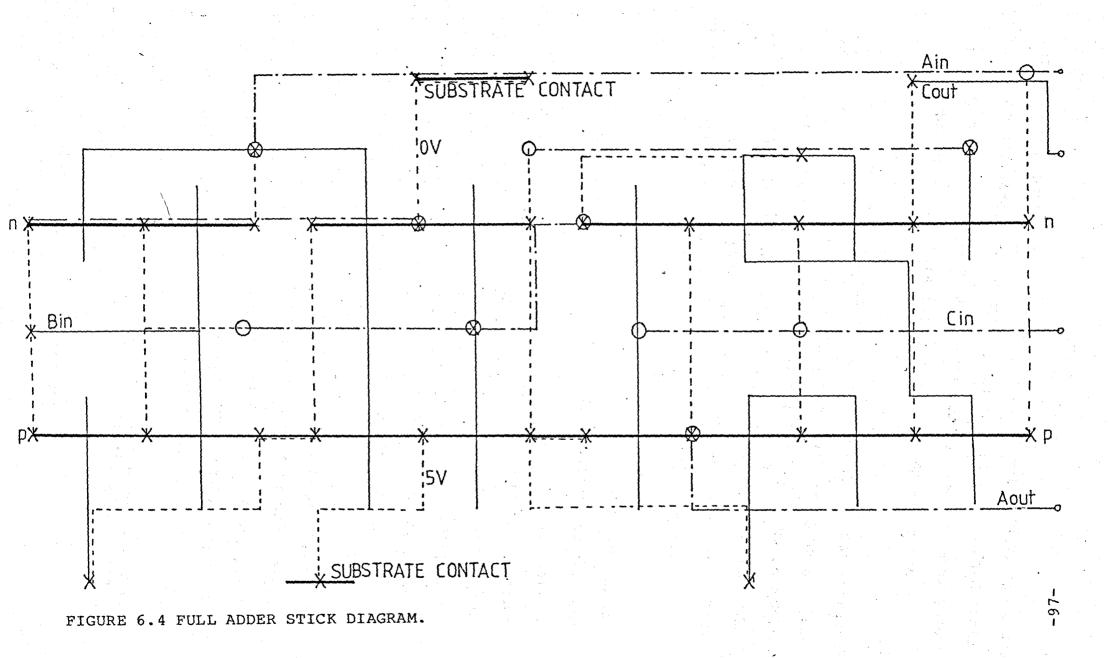

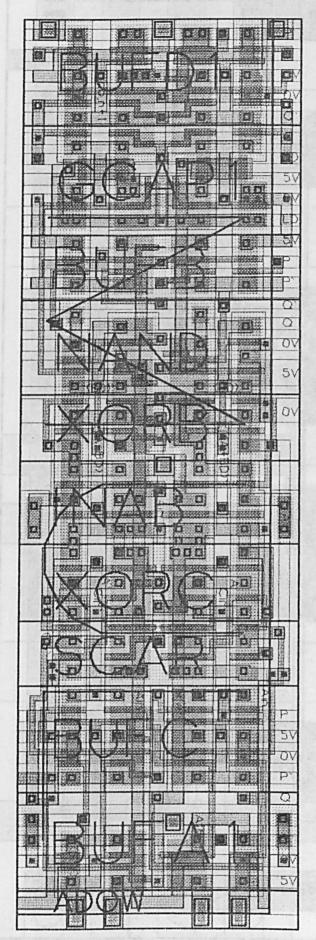

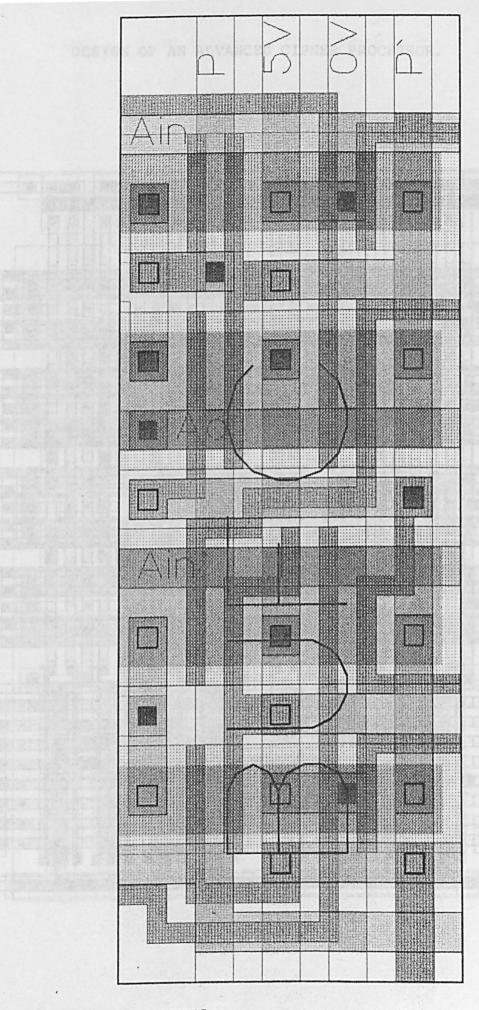

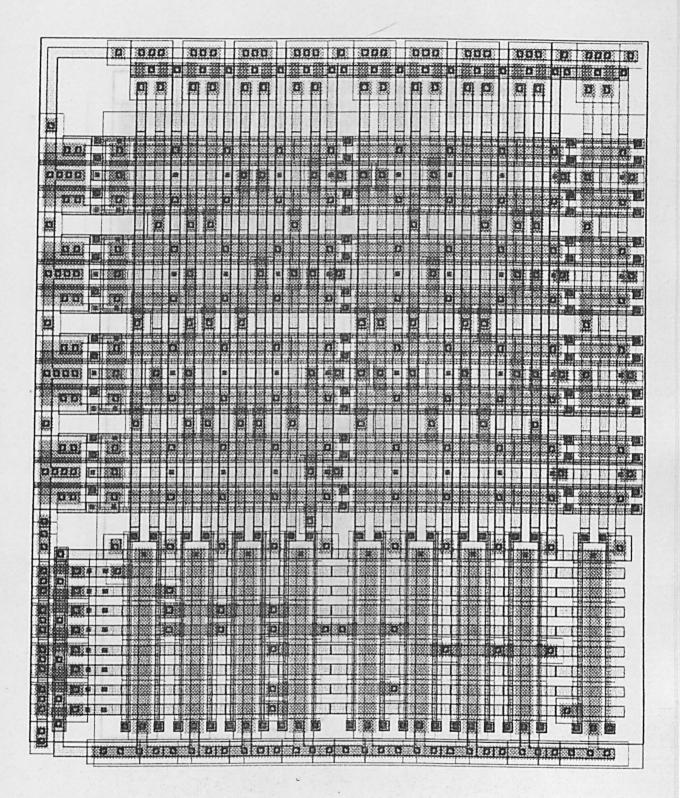

Chapter six describes the potential and pitfalls of VLSI, followed in chapter seven by a model for comparing the cost and performance of VLSI architectures. Chapter eight deals with novel architectures for all the basic arithmetic operations. These architectures provide a basic vocabulary of low complexity VLSI arithmetic structures for a wide range of applications.

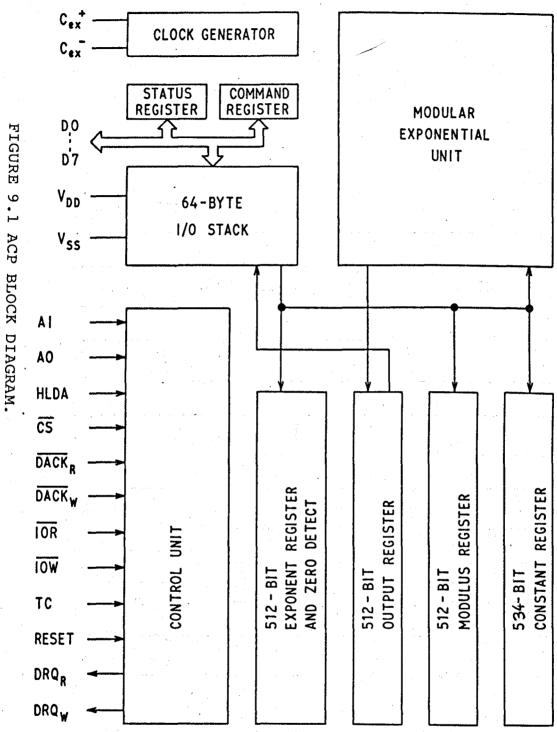

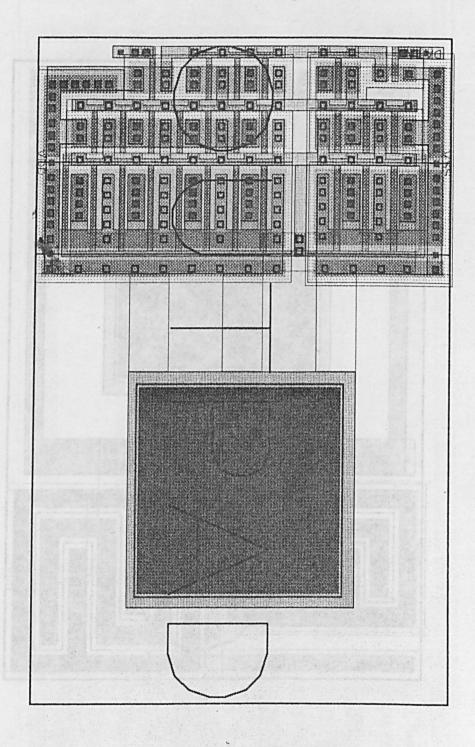

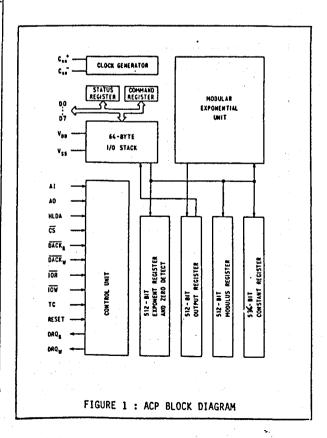

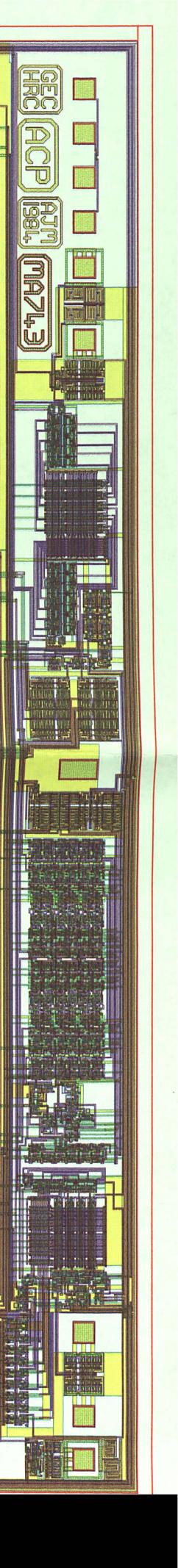

The design of a VLSI device, the Advanced Cipher Processor (ACP), to implement the RSA algorithm is described in chapter nine. It's heart is the modular exponential unit, which is a synthesis of the architectures in chapter eight. The ACP is capable of a throughput of 50 000 bits per second.

-2-

PREFACE

PREFACE.

Until fairly recently, the science of keeping information secret remained almost totally unknown outside the military and diplomatic communities. Even today most people only think of the romantic work of the codebreaker of cryptanalyst, whose efforts during WWII provided such a vital source of intelligence to the Allies. But in recent years there is increasing interest in the reciprocal science of the codemaker or cryptographer. This thesis is concerned with the latter; a challenging and exciting area of research.

Cryptography unites the diverse fields of electronics, pure mathematics and computer science. Although this thesis is written primarily for the electronics engineer, it is necessary to call on areas outside their usual knowledge. Therefore, Chapter 1, as well as introducing the basic cryptographic techniques, will provide an introduction to Galois fields, number theory and computational complexity. Those familiar with cryptography might still find it useful to familiarize themselves with the notations used in later chapters.

Cryptography has been revolutionized by two developments in the last ten years. Firstly, the concept of the Public Key Cryptosystem (PKC), which greatly enhances the capabilities offered. Secondly, the pervasive technology of Very Large Scale Integration (VLSI), which gives substance and impetus to these new ideas. The thesis covers the author's original work in the

-1-

### PREFACE

design, application and implementation of cryptography to business and commercial telecommunication systems. A digest of these chapters is given below.

CHAPTER 2. Describes a generalization of the original Merkle-Hellman trapdoor knapsack PKC. A new scheme is proposed which allows reduced redundancy and a smaller public key directory.

CHAPTER 3. Puts forward a new trapdoor for the general knapsack PKC. It is based on the transformations between radix and residue number systems. The security does not rely on transformations from a superincreasing sequence, which have proven vulnerable to cryptanalysis.

CHAPTER 4. Describes how cryptography can efficiently be applied to information intended for more than one receiver. It shows how the natural security or communications network structure can be exploited, together with a new concept: the broadcast cryptosystem. The latter allows a message to be deciphered by more than one receiver, if reduced, security can be tolerated.

CHAPTER 5. Describes how cryptography can be applied to enforce copyright protection on a wide range of published material. The bases of the proposed solutions are the combination of tamper resistant modules and a PKC.

CHAPTER 6. Looks at the whole design cycle for a custom VLSI chip. It draws attention to the particularly important aspects the author has found in such a design.

CHAPTER 7. Describes a comprehensive model for designing

-2-

### PREFACE

VLSI architectures. This model is intended to be adaptable to new technologies.

CHAPTER 8. Describes some new VLSI architectures for realizing the basic arithmetic functions used in digital signal processing. It concentrates on maximizing their asymptotic performance and minimizing design complexity.

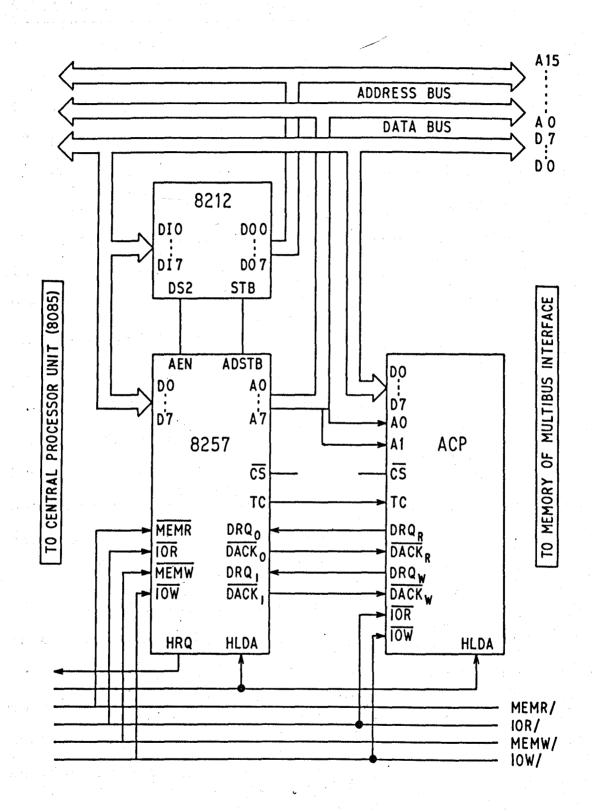

CHAPTER 9. Describes the implementation of the RSA-PKC in CMOS. The finished design is a 24-pin DIL package, with Multibus interface.

CHAPTER 10. Draws conclusions from previous chapters and makes forecasts for the future.

One important point, which has not changed over the centuries, is that security is very difficult to gauge. The interpretations drawn should be read with a spark of scepticism. For in one hundred years, many interpretations may be regarded as erroneous.

The author wishes to thank all those who directly or indirectly contributed to this thesis. In particular, I am grateful to my supervisor, Dr R. Goodman, who has been a constant source of ideas and encouragement. I would also like to extend my appreciation to my colleages at Hirst Research Centre for their guideance on the VLSI apsect of my research. Especially to Mike Rome, Andrew McCabe and Nick Parker.

-3-

# CONTENTS.

| 1. | . BASIC TECHNIQUES.                             | 10 |

|----|-------------------------------------------------|----|

|    | 1.1 Introduction.                               | 11 |

|    | 1.2 Terminology and mathematical notation.      | 12 |

|    | 1.3 Mathematical background.                    | 13 |

|    | 1.3.1 Some properties of a ring of integers.    | 15 |

|    | 1.3.2 Residue arithmetic.                       | 17 |

|    | 1.4 Cryptanalysis and computational complexity. | 18 |

|    | 1.4.1 Measure of performance.                   | 19 |

|    | 1.4.2 NP problems.                              | 19 |

| •  | 1.4.3 Cryptographically secure.                 | 20 |

|    | 1.5 Cryptographic techniques.                   | 22 |

|    | 1.5.1 Public key cryptosystems.                 | 22 |

|    | 1.6 Practical Public Key Cryptography.          | 26 |

|    | 1.6.1 DH key distribution scheme.               | 27 |

|    | 1.6.2 MH trapdoor knapsack PKC.                 | 28 |

|    | 1.6.3 RSA modular exponential PKC               | 29 |

|    | 1.7 References.                                 | 31 |

|    |                                                 |    |

|    |                                                 |    |

| 2. | A GENERAL KNAPSACK PROBLEM.                     | 36 |

|    | 2.1 Introduction.                               | 37 |

|    | 2.2 Notation.                                   | 38 |

|    | 2.3 The general method.                         | 39 |

|    | 2.4 The effect of parameter selection.          | 40 |

|    |                                                 |    |

-4-

| 42 |

|----|

| 43 |

| 43 |

| 45 |

| 45 |

| 46 |

| 47 |

|    |

|    |

| 49 |

| 50 |

| 51 |

| 52 |

| 55 |

| 57 |

| 57 |

| 57 |

| 58 |

| 59 |

|    |

| 60 |

| 61 |

| 61 |

| 62 |

| 63 |

| 64 |

| 64 |

| 68 |

|    |

| 4.6 Conclusion. |  |  | 70 |

|-----------------|--|--|----|

| 4.7 Reference.  |  |  | 71 |

|                 |  |  |    |

| 5. ELECTRONIC PUBLISHING AND COPYRIGHT PROTE | ECTION. 72 |

|----------------------------------------------|------------|

| 5.1 Introduction.                            | 73         |

| 5.2 Electronic publishing.                   | 73         |

| 5.3 Copyright and cryptography.              | 74         |

| 5.4 Software protection.                     | 75         |

| 5.4.1 Tamper resistant microcompute          | er. 76     |

| 5.5 Gener al information security.           | 78         |

| 5.5.1 Fingerprinting.                        | 78         |

| 5.5.2 Broadcast reception.                   | 82         |

| 5.6 Conclusion.                              | 82         |

| 5.7 References.                              | 83         |

|                                              |            |

|                                              | · · · · ·  |

| 6. LOW COMPLEXITY CUSTOM VLSI DESIGN.        | 85         |

| 6.1 Introduction.                            | 86         |

| 6.2 Top down design.                         | 87         |

| 6.2.1 Simulation.                            | 88         |

| 6.2.2 Documentation.                         | 88         |

| 6.3 System design.                           | 89         |

| 6.4 Architecture design.                     | 89         |

| 6.5 Circuit design.                          | 91         |

| 6.6 Layout design.                           | 95         |

| 6.6.1 Stick diagram.                         | 98         |

| 6.6.2 Checking.                              | 99         |

| r                          |                                          |     |

|----------------------------|------------------------------------------|-----|

| 6.7 Testing and redesign.  |                                          | 99  |

| 6.8 Conclusion.            |                                          | 100 |

| 6.9 References.            |                                          | 101 |

|                            |                                          |     |

|                            |                                          |     |

| 7.GOOD VLSI ARCHITECTURES. | n an | 104 |

| 7.1 Introduction.          |                                          | 105 |

| 7.2 VLSI models.           |                                          | 106 |

| 7.3 Performance.           |                                          | 106 |

|                            |                                          |     |

| 7.4 Design costs.                          | 107 |

|--------------------------------------------|-----|

| 7.5 Manufacturing costs.                   | 107 |

| 7.6 Characteristics of VLSI architectures. | 108 |

| 7.7 Conclusion.                            | 110 |

| 7.8 References.                            | 111 |

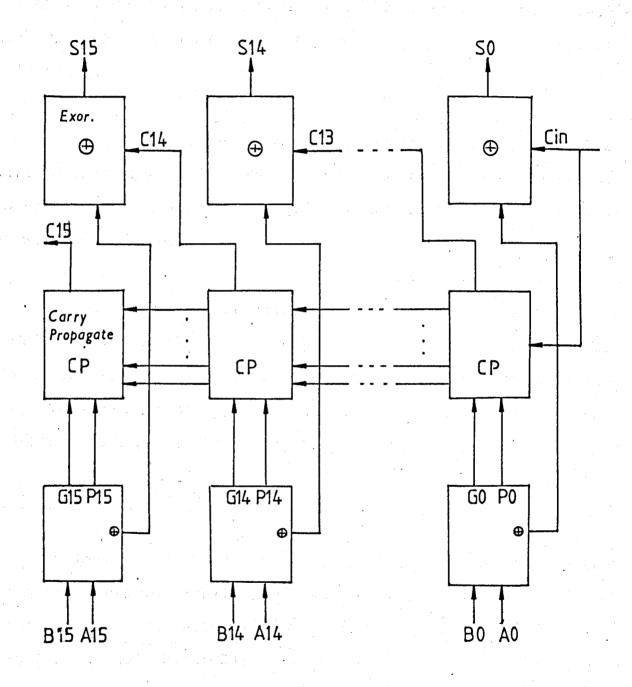

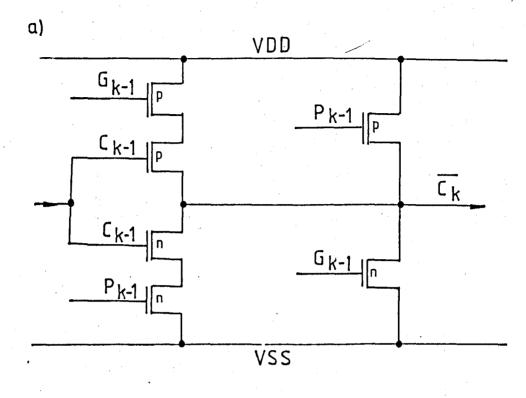

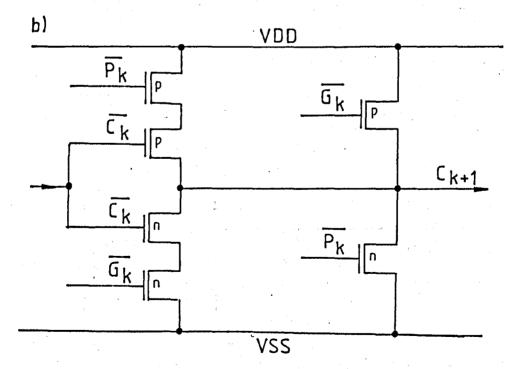

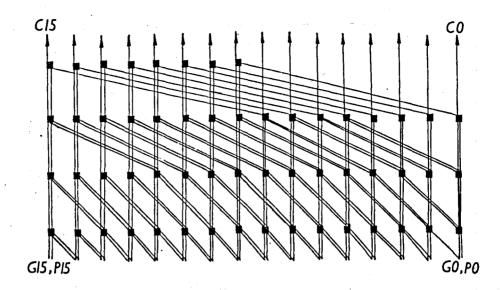

| 8. ARITHMETIC ARCHITECTURES.          | · | 112 |

|---------------------------------------|---|-----|

| 8.1 Introduction.                     |   | 113 |

| 8.2 Arithmetic on silicon.            |   | 113 |

| 8.3 Addition and subtraction.         |   | 114 |

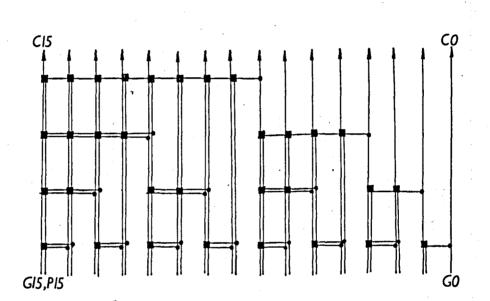

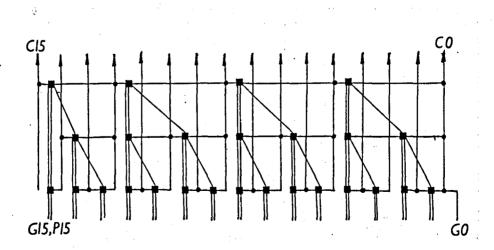

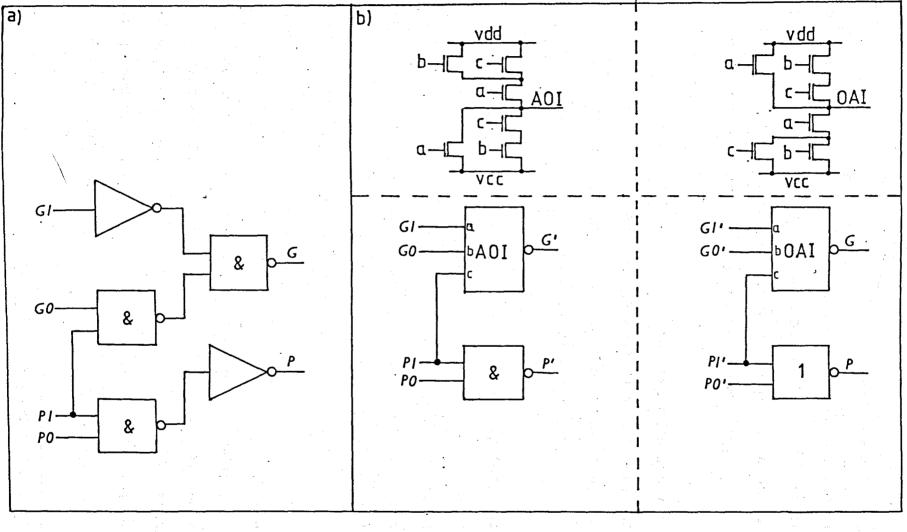

| 8.3.1 Fast carry propagation schemes. |   | 116 |

| 8.3.2 Manchester carry chain.         |   | 117 |

| 8.3.4 Carry look-ahead adder.         |   | 121 |

| 8.3.5 Conditional sum adder.          |   | 122 |

| 8.3.6 Carry bypass adder.             |   | 122 |

| 8.3.7 Testing the adder.              |   | 122 |

| 8.3.8 Performance comparison: adders. |   | 123 |

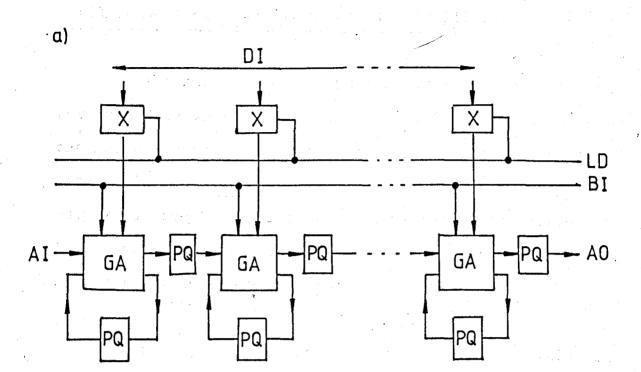

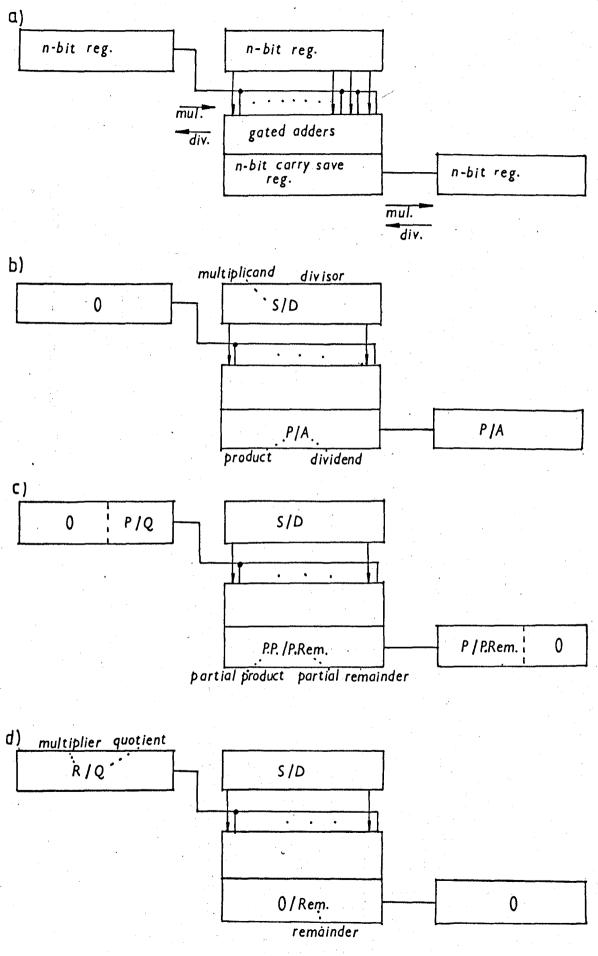

8.4 Multiplication.

-7-

. 124

| 8.4.1 Conventional serial-parallel multiplier.  | 126 |

|-------------------------------------------------|-----|

| 8.4.2 New serial-parallel multiplier.           | 127 |

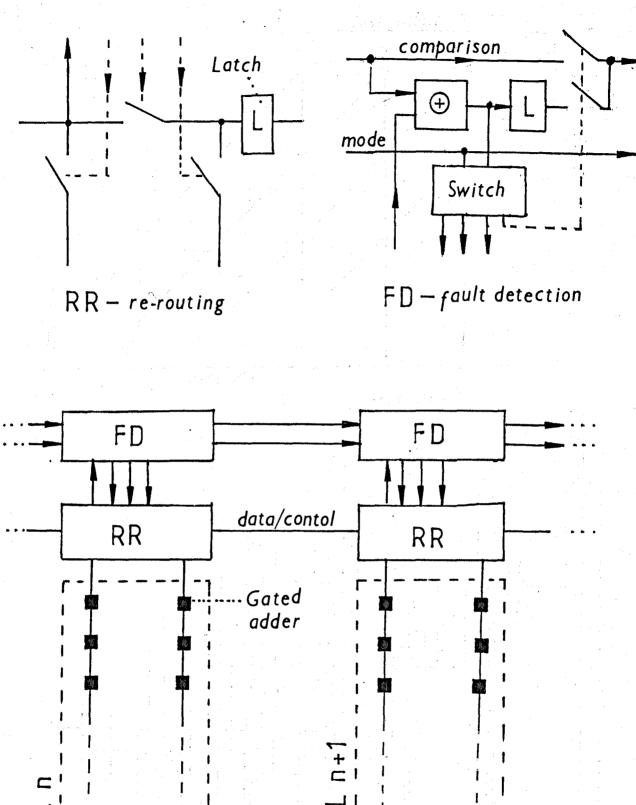

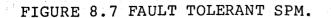

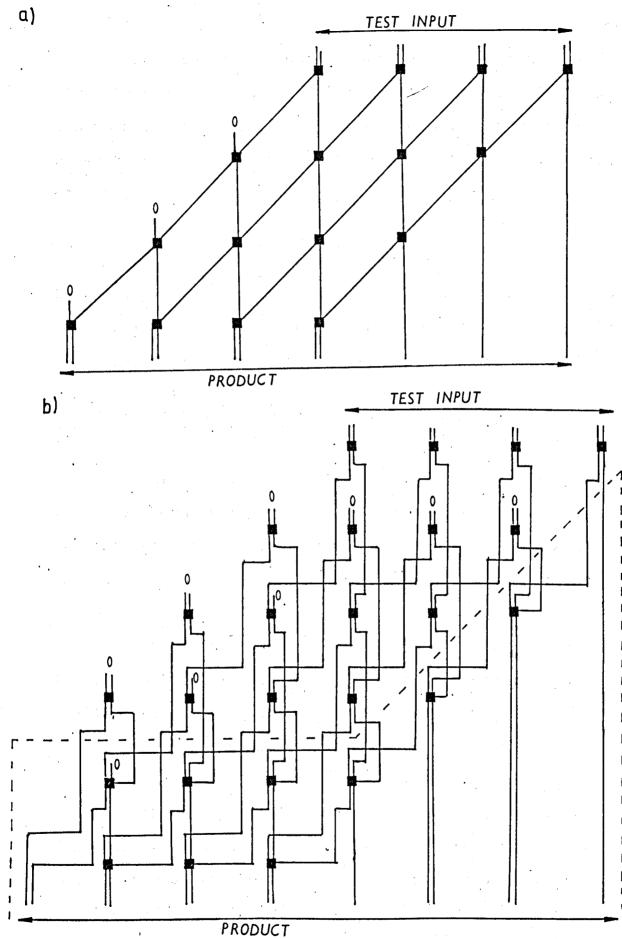

| 8.4.3 Testing the SPM.                          | 128 |

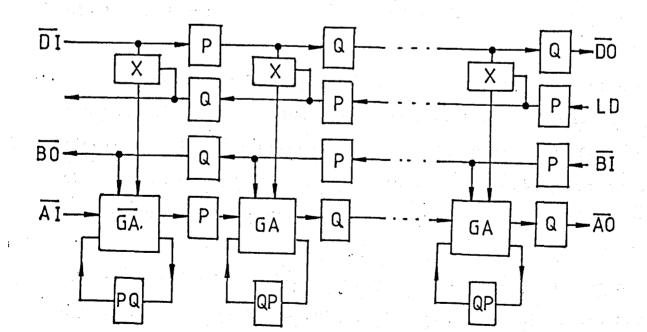

| 8.4.4 Fault tolerance with the SPM.             | 128 |

| 8.4.5 Parallel multiplier.                      | 131 |

| 8.4.6 New parallel multiplier.                  | 132 |

| 8.4.7 Testing the PM.                           | 132 |

| 8.4.8 Performance comparison: multipliers.      | 133 |

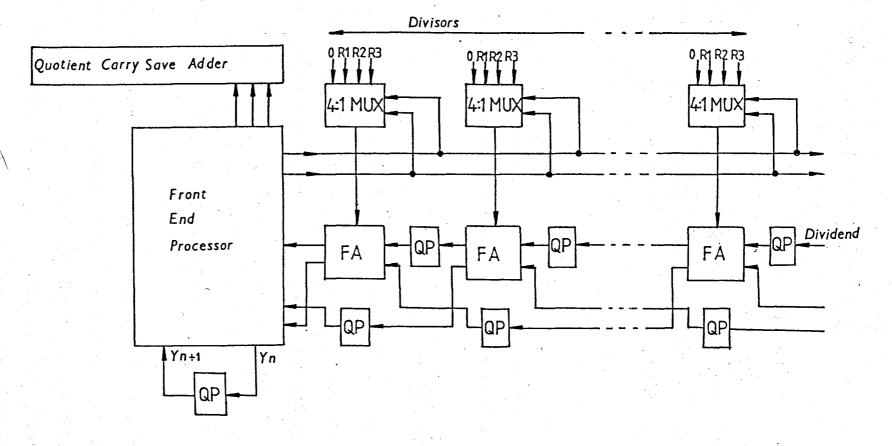

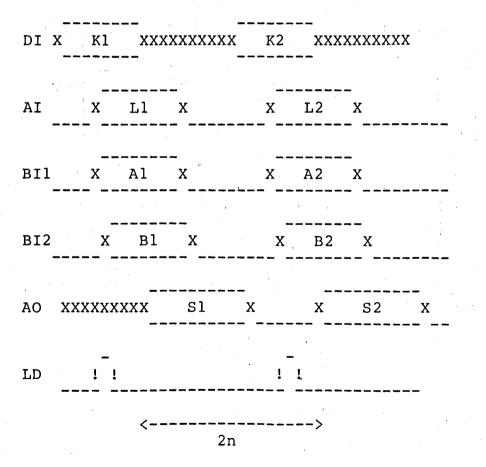

| 8.5 Division.                                   | 134 |

| 8.5.1 Principle of the serial-parallel divider. | 135 |

| 8.5.2 A practical SPD.                          | 138 |

| 8.5.3 Performance comparison: dividers.         | 140 |

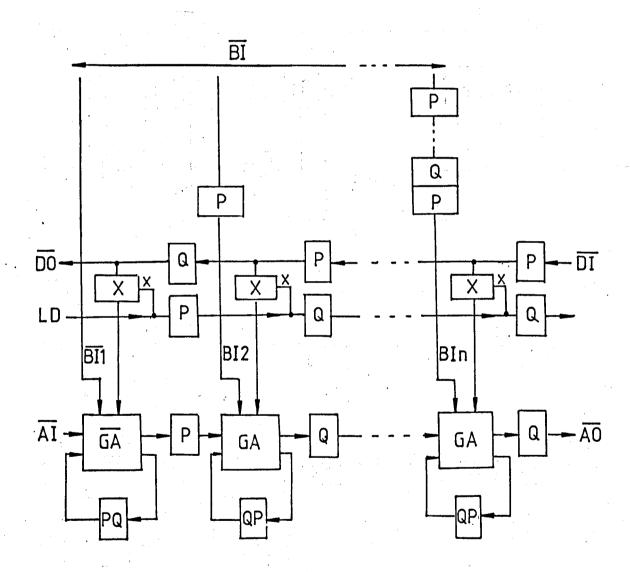

| 8.6 Modular multiplication.                     | 140 |

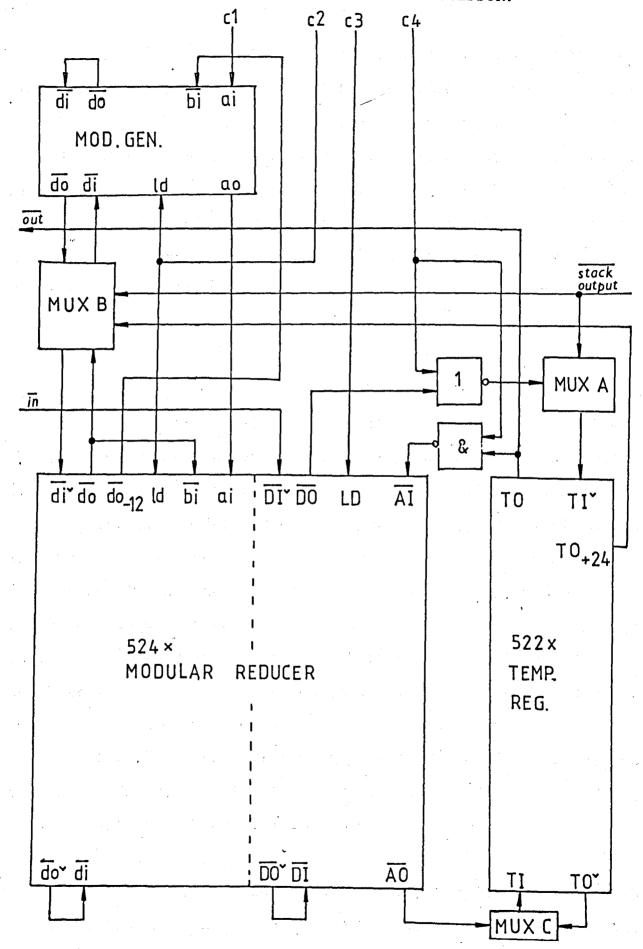

| 8.7 Modular reduction.                          | 144 |

| 8.8 Synthesizing the required funtion.          | 146 |

| 8.9 Conclusion.                                 | 148 |

| 8.10 References.                                | 150 |

|                                                 |     |

| 9. DESIGN OF AN ADVANCED CIPHER PROCESSOR.      | 154 |

| 9.1 Introduction.                               | 155 |

| 9.2 History.                                    | 156 |

| 9.3 System design.                              | 157 |

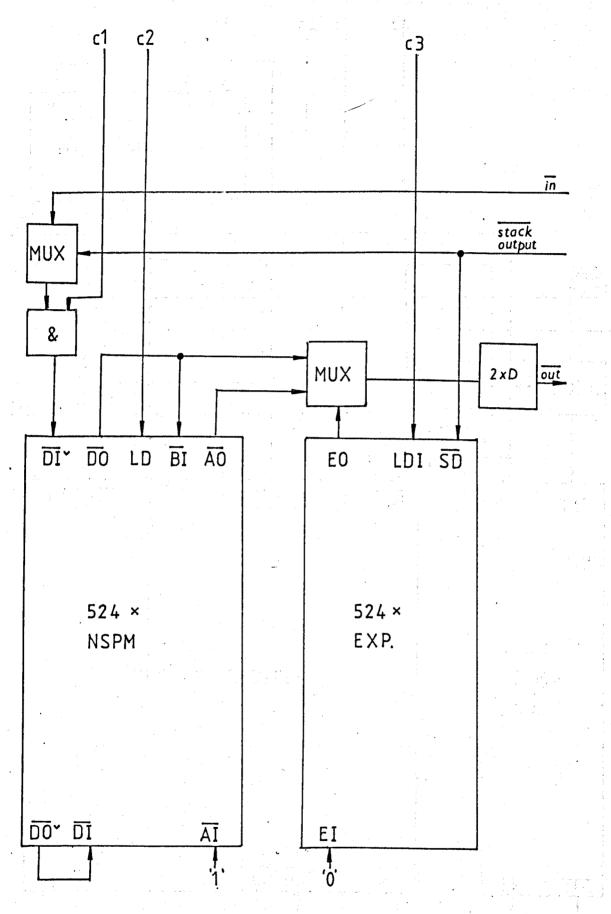

| 9.3.1 Modular exponential unit.                 | 162 |

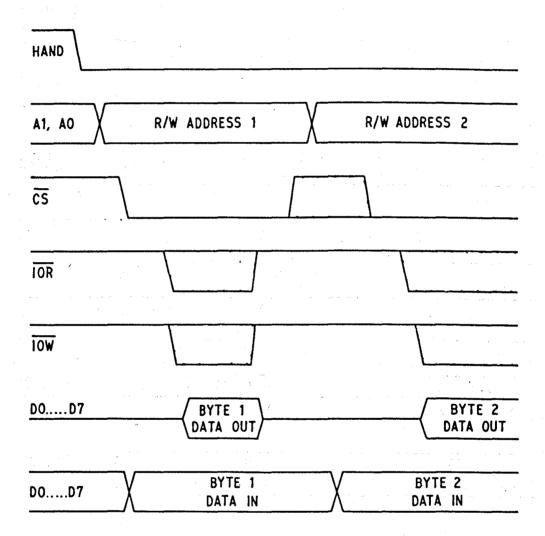

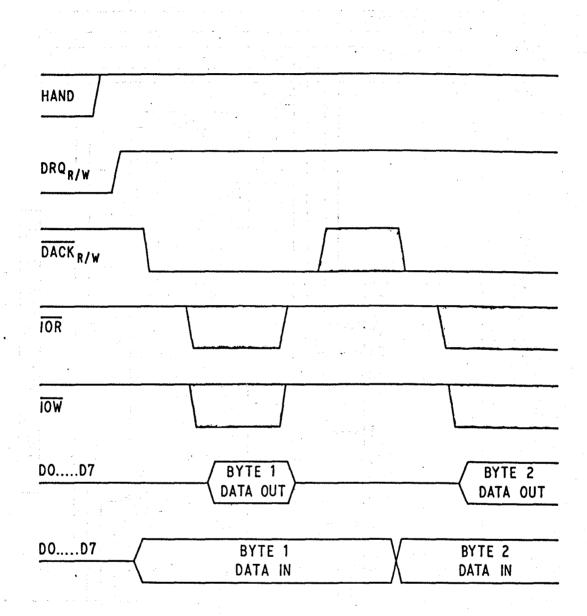

| 9.3.2 Interface.                                | 162 |

| 9.3.3 Synchronization.                          | 163 |

| 9.3.4 Control unit.                             | 165 |

| 9.3.5 Stack.                                    | 165 |

|                                                 |     |

-8-

| 9.4 Architecture design.                  | 167 |

|-------------------------------------------|-----|

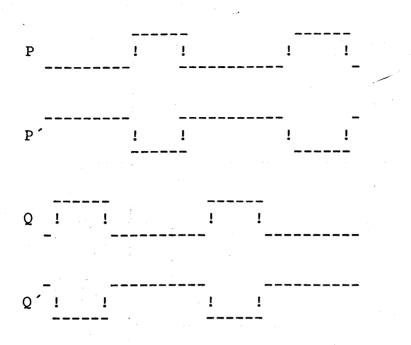

| 9.4.1 Clock generator and buffer.         | 167 |

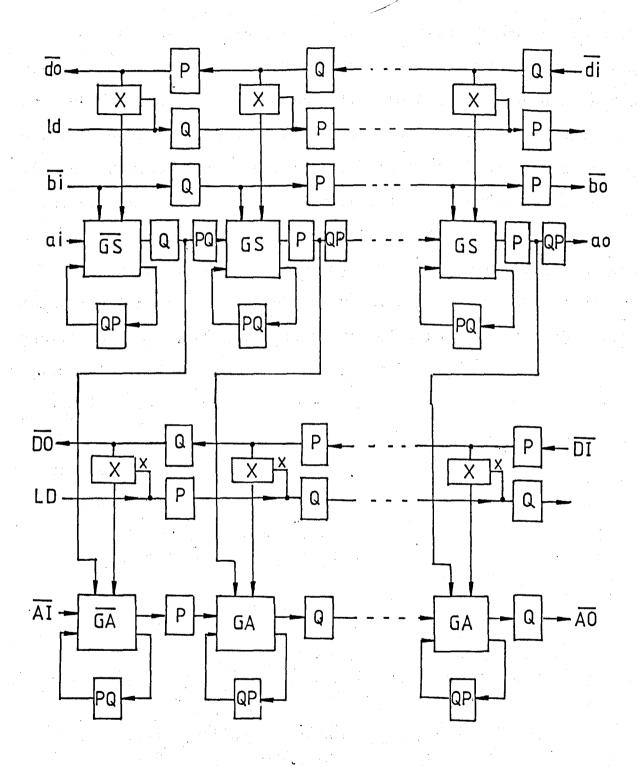

| 9.4.2 Modular exponential unit.           | 168 |

| 9.4.3 External logic.                     | 174 |

| 9.4.4 Control unit.                       | 175 |

| 9.4.5 Stack.                              | 179 |

| 9.4.6 Waveform generator.                 | 180 |

| 9.4.7 Serial divider and output register. | 181 |

| 9.4.8 Other registers.                    | 185 |

| 9.5 Circuit design.                       | 185 |

| 9.5.1 Gated adder and subtractor.         | 186 |

| 9.5.2 Static and dynamic latches.         | 186 |

| 9.5.3 Crystal oscillator.                 | 186 |

| 9.5.4 Phase splitter and buffer.          | 189 |

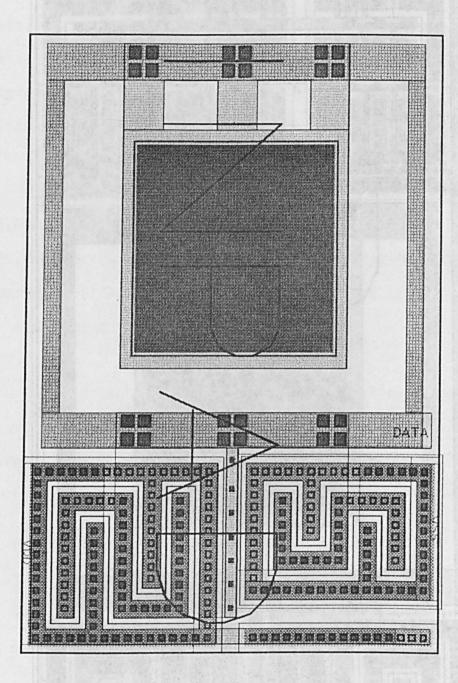

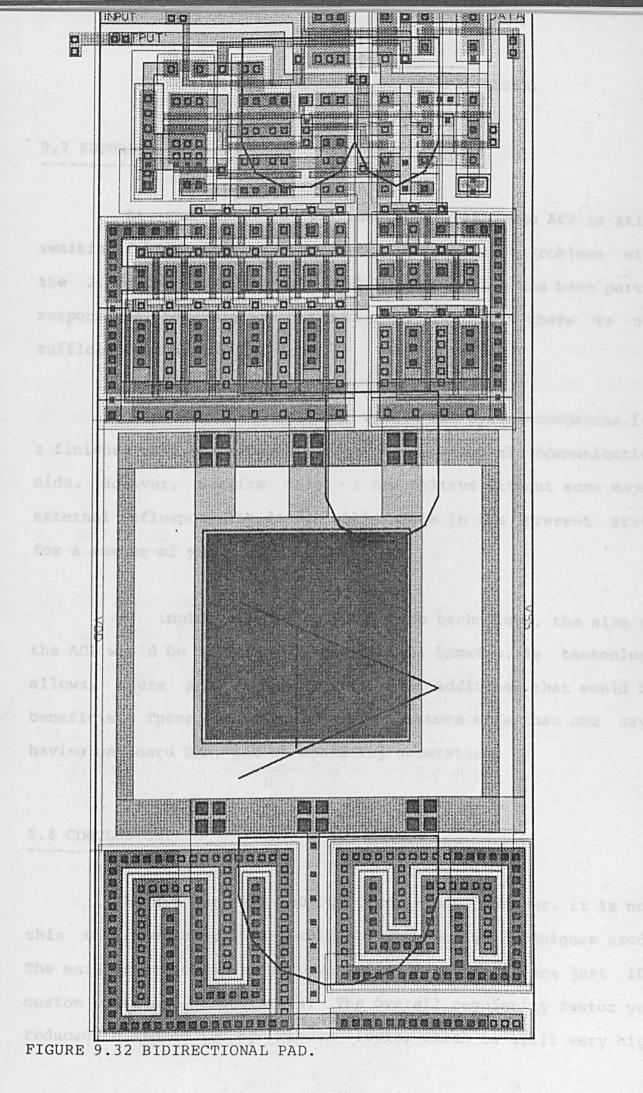

| 9.5.5 Pads.                               | 189 |

| 9.5.6 Programmable logic arrays.          | 193 |

| 9.5.7 Random logic.                       | 193 |

| 9.6 Layout.                               | 194 |

| 9.7 Future.                               | 207 |

| 9.8 Conclusion.                           | 207 |

| 9.9 References.                           | 208 |

|                                           |     |

|                                           |     |

| 10. SUMMARY AND FORECAST.                 | 211 |

|                                           |     |

| PAPERS PRESENTED BY THE AUTHOR.           | 218 |

| ABBREVIATIONS.                            | 220 |

# CHAPTER

### 1.1 INTRODUCTION.

Many people think they could invent a perfect cipher. But a brief look through the history of cryptography (Ref.101) teaches caution. Though many systems have served their purpose for a brief period of time, the cryptanalyst has always proven too resourceful. However with the aid of cheap hardware, increased sophistication and more open discussion, it is now possible to talk of a cipher that will remain secure for a very long time.

This chapter introduces the basic techniques which are helping to achieve greater confidence in cryptography. It is aimed at covering the salient features which relate to subsequent chapters.

No attempt is made to cover the whole spectrum of modern cryptography. It only scratches the surface of important areas such as: secret sharing, standards, analogue techniques and cryptanalytic methods.

The thesis assumes an understanding of the recent advances in cryptography. Those unfamiliar with these developments are referred to one of the many excellent digests available in the literature (Refs.102-111).

-11-

### 1.2 TERMINOLOGY AND MATHEMATICAL NOTATION.

The problem of understanding a highly specialized subject is always hindered by the use of words used only in its limited field. Hopefully most such words will be explained when they are used, but the following brief list might be useful.

AUTHENTICITY: Determine the integrity of data and transmitter.

BREAKABLE SYSTEM: A cryptosystem where it is possible to cryptanalyse the ciphertext.

CIPHERTEXT: Secret form of a message.

CRYPTOLOGY: The science of transmission security, encompassing both cryptography and cryptanalysis.

CRYPTOGRAPHY: Science of rendering information intelligible only to a legitimate receiver.

CRYPTANALYSIS: Science of the techniques used to decipher ciphertexts, without the secret key.

CRYPTOSYSTEM: Method of hiding information, using a known algorithm and secret key.

ENCIPHER: To convert a message from plaintext to ciphertext.

KEY: Information needed to encipher/decipher a message/ciphertext.

MESSAGE/PLAINTEXT: Information in readable form.

SECURITY: Computational feasiblity of deciphering a message, without the secret key.

-12-

A list of abbreviations used in the following chapters is given at the end the thesis. In addition, a number of non-standard mathematical shorthands will be used. These are listed below.

= (l if n = 0, else

(biggest integer less than or equal to  $\log n$ )

A xor B = A.B' + A'.B

A >= B. A is greater than or equal to B.

$A \leq B$ . A is less than or equal to B.

A <> B. A not equal to B.

A >> B. A is very much greater than B.

A << B. A is very much less than B.

A = B. A is approximately equal to B.

## 1.3 MATHEMATICAL BACKGROUND.

A cryptosystem can be thought of as a set of transformations, from the set of possible messages into the set of possible ciphertexts. Each transformation will correspond to encipherment with a particular key. For cryptographic applications these transformations must be injective and ideally bijective. In the PKCs considered here, these transformations are defined by simple arithmetic functions.

-13-

In order to keep the size of the cryptosystem within bounds, the arithmetic is either done in the Galois fields  $GF(2^n)$ , GF(p) or the ring R(q): where p is a prime and q is the product of primes. This has the added advantage of making cryptanalysis more difficult, since it both reduces the amount of information and introduces an extra element of diffusion. More information on these algebraic systems can be obtained in the literature (Refs.112-113).

Arithmetic in  $GF(2^n)$  is always done mod p(x): where p(x) is an irreducible polynomial of degree n. Figure 1.1a gives an example of how two numbers can be added and multiplied. Arithmetic in R(n) is done mod n; figure 1.1b gives an example of how the same operations are done here.

| ~~~~~~~~                          |                    |

|-----------------------------------|--------------------|

| 1001 !<br>+ 1011 !<br>!<br>0010 ! | 1001<br>* 1011<br> |

| ADDITION !                        | + 0000<br>+ 1001   |

| !<br>!<br>!                       | 1010011<br>- 10001 |

| 1001<br>- 1011                    | - 00000<br>- 10001 |

| 0010                              | 0110               |

| SUBTRACTION !                     | MULTIPLICATION     |

|                                   | **********         |

FIGRE 1.1a ARITHMETIC IN GF(2<sup>4</sup>), WITH IRREDUCIBLE P(X) = 10001.

-14-

| 1001<br>+ 1011<br><br>10100<br>- 1111<br> | !<br>! 1001<br>* 1011<br>!<br>! 1001<br>! + 1001<br>! + 0000 |

|-------------------------------------------|--------------------------------------------------------------|

| 0101                                      | ! + 1001                                                     |

| ADDITION                                  | !<br>! 01100011<br>! _ 0000<br>! _ 0000                      |

|                                           |                                                              |

| 1001                                      | <u> </u>                                                     |

| - 1011                                    | 1                                                            |

|                                           | 1001                                                         |

| 11110                                     |                                                              |

| + 1111                                    | ·                                                            |

|                                           | MULTIPLICATION                                               |

| 1101                                      | <u>1</u>                                                     |

|                                           | 1                                                            |

| SUBTRACTION                               |                                                              |

|                                           |                                                              |

FIGURE 1.1b ARITHMETIC IN R(15).

An important difference between the two systems is that in GF(2<sup>n</sup>) there are no carries. This allows faster and simpler implementations, but does reduce the desirable element of confusion. Because of this latter point, systems based on GF(2<sup>n</sup>) will not be considered here.

1.3.1 Some properties of a ring of integers.

In the ring R(n) only integers between 0 and n-1 are allowed. If the results are larger or smaller than this, then the answer is found by reducing modulo n.

Division is not strictly a ring operation, since only

integer results are allowed. The equivalent ring operation is called inversion. For a given number (x), this involves finding another number (y) with the property:

$x * y = 1 \mod n$

This operation is not possible if x is a factor of n.

For the ring R(n), a key parameter is the Euler totient function U(n). This is the number of integers which are relatively prime to n. Let n be the product of k primes:

$$n = \prod_{i=1}^{k} p_{i}, \text{then}$$

$$U(n) = \prod_{i=1}^{k} (p-1)_{i}$$

For an integer x, it can be shown that:

U(n)x mod n = 1, if GCD (x,n) = 1 If x \* y = 1 mod n

$\begin{array}{c} U(n) - 1\\ \text{then } y = x \end{array}$

...1.1

...1.2

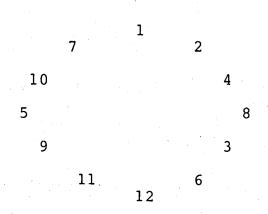

FIGURE 1.2 RING R(13).

-16-

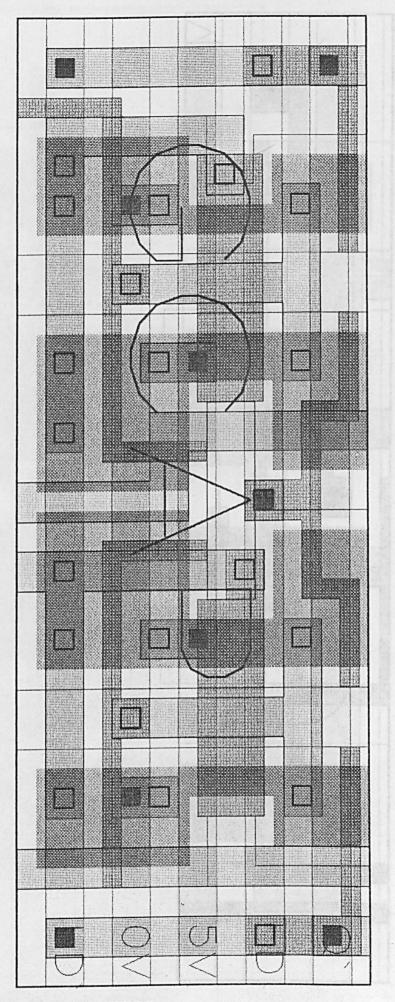

An interesting way of looking at the ring R(13) is shown in figure 1.2. Each number, going clockwise round the circle, is twice (mod 13) the previous number. From this diagram we see:

$$U(13) = 12$$

, the size of the circle.

$3 = 8$ , at three o'clock.

$12 = 2 = 1$ , at twelve o'clock (equation 1.1).

$11 = U(13)-1$

$2 = 2 = 7$ , where 2 \* 7 = 1 (equation 1.2)

A more computationally efficient method of finding the inverse is to use Euclid's extended algorithm (Ref.114). Inverses always exist if GCD (x,n) = 1.

1.3.2 Residue arithmetic.

In its residue form a number in R(n) is represented by its remainders, when divided by the factors of n. For a number xlet:

$\begin{array}{c} \text{(i)} \\ \text{x} &= \text{x mod } \text{p} \\ \text{i} \end{array}$

Then by the Chinese Remainder Theorem (Ref.115):

(1) (2) (k) x < --> x , x , ... , x

is a bijective mapping. That is the transformation is one-to-one for all x's between 1 and n-1.

The ring R(n) can be represented in radix or residue

form: the two forms being homomorphic. The radix form is the 'normal' way of representing a number. However the residue form has a number of advantages.

In the residue form arithmetic can easily be split up, allowing greater parallelism. In chapter 3 we shall show how the residue form of a number can be useful for cryptography. Figure 1.3 shows how the basic arithmetic operations are performed, in both radix and residue number systems.

| mod mod mod<br>15 5 3      |                                   |

|----------------------------|-----------------------------------|

| 8 <> 3, 2<br>+ 11 <> 1, 2  | 8 <> 3, 2<br>* 11 <> 1, 2         |

| 4 <> 4 , 1<br><br>ADDITION | 13 <> 3 , 1<br><br>MULTIPLICATION |

|                            | •                                 |

FIGURE 1.3 ARITHMETIC IN RADIX AND RESIDUE FORM.

# 1.4 CRYPTANALYSIS AND COMPUTATIONAL COMPLEXITY.

Cryptanalysis is concerned with finding an optimum way of breaking a cipher. This is usually expressed in terms of the computational complexity of the algorithm used to solve it.

Complexity is measured in terms of time and area: where area is the number of processors and memory used (Ref.115).

-18-

# 1.4.1 Measure of performance.

How can we measure the goodness of one algorithm or architecture against another? A useful shorthand is the 'big O' notation. An algorithm f(n) is said to be of order O(g(n)) if there exists some constant c such that f(n) < c(g(n)). For example the function:

7 3 7 8n + 3n + logn, is O(n) and the function 7n.logn + 5n + 9, is O(n.logn)

An algorithm of higher order of magnitude might have a smaller constant of proportionality. In which case, the higher order algorithm might be superior for slower or smaller machines. However the asymptotic complexity is a good measure, and one that becomes increasingly important as technology advances.

The use of 'order statistics' allows a designer to concentrate on the important issues. For example a 32-bit microprocessor might be very much faster than an 8-bit one, but an algorithm O(n) for one machine will be O(n) on the other.

1.4.2 NP problems.

Algorithms of O(k<sup>n</sup>) have an explosive rate of growth. There is general agreement that problems requiring an algorithm with this exponential growth are intractable (Ref.115). A problem of this form is known as a non-deterministic polynomial problem:

-19-

denoted by NP.

There are a class of problems which are NP-complete. That is, if one problem can be solved in polynomial time, they all can (Ref.115). The solution of an NP problem is often the target which a cryptographer tries to give a cryptanalyst. But it is important to realize that NP-complete refers to only the hardest instances of a problem.

1.4.3 Cryptographically secure.

The definition of cryptographic security might be that it is impossible to cryptanalyse a message. However this is unnecessarily restrictive; indeed only the one time pad posseses this property (Ref.101). Consider a computer operating: 1. Using every atom (10<sup>100</sup>) in the universe as a Processing

Element.

2. Each Processing Element operating in the time required by light to traverse a nuclear radius (10<sup>-23</sup> seconds).

3. Been operating since the beginning of the universe (4 \* 10<sup>10</sup> years).

Using this rather conservative model, the computer could still not have finished an algorithm requiring 2<sup>500</sup> steps. For cryptographic intractablity, a figure of 2<sup>128</sup> is sufficient.

-20-

TRANSMITER ---- CHANNEL ----- RECEIVER

# ---Shielding

FIGURE 1.4 ONE AND TWO KEY CRYPTOSYSTEMS.

# 1.5 CRYPTOGRAPHIC TECHNIQUES.

In modern cryptography, the security of a transmission lies in keeping the key secure, rather than the whole system. This not only allows greater confidence in a cryptosystem, but permits the adoption of standards (Ref.111).

In a conventional cryptosystem, such as the US Data Encryption Standard (DES), the keys used for encryption and decryption are the same (see figure 1.4a). However such a system leads to a key distribution problem. A network with 2000 users would require over 2 million keys to allow each user to talk to every other.

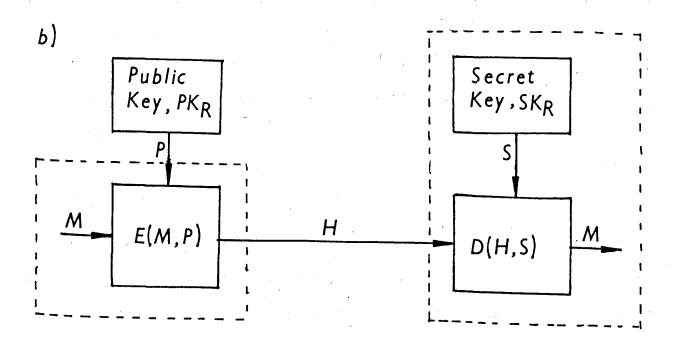

A recent scheme proposed by Diffie and Hellman (Ref.116) overcomes the key distribution problem. It does so by using a different key for encryption and decryption (see figure 1.4b). This use of asymmetric keys has become known as a Public Key Cryptosystem (PKC).

# 1.5.1 A Public Key Cryptosystem.

The PKC derives its name from the fact that it publishes the encryption key (Public Key, PK), but keeps the decryption key hidden (Secret Key, SK). To help understand this principle, an analogy is useful.

A room is full of English speaking people, none of whom

-22-

speak French. The Engish to French half of a language dictionary is freely available; but someone has destroyed all but one copy of the French to English half. In this scenario anyone can write a message in French. However only the person who has the French to English dictionary could decipher these messages.

In the above analogy the English to French dictionary represents the encryption function and the French to English dictionary the decryption function. It is possible to break the system by searching the English to French dictionary. But in a good cryptosystem the analogous operation would be too computationally demanding.

Encryption and decryption can be expressed mathematically by equations 1.3 and 1.4.

Sender, S: e(Ml, PK) = C ...1.3 R Receiver, R: d(Cl, SK) = Ml ...1.4

Where e(X,K) denotes encryption and d(X,K) decryption of a message X under a key K. The two functions are not necessarily different.

A PKC is not only able to offer WRITE ONLY communication with easy key distribution. The real power of PKC stems froms its ability to offer READ ONLY communication.

If the sender transforms a message M2 under his own

secret key, anyone can look up the public key to recover M2. But since only the sender has the secret key, only he could generate a message 'deciphered' under it. This operation, which is equivalent to a written signature, is described by equations 1.5 and 1.6.

Sender, S: d(M2,SK) = C2 ...1.5 Receiver, R: e(C2,PK) = M2 ...1.6 It is possible to combine read and write only protection: Sender, S: e(d(M3,SK),PK) = C3 ...1.7 Receiver, R: d(e(C3,PK),SK) = M3 ...1.8

Using the transformations described above it is possible to protect against both active and passive eavesdropping.

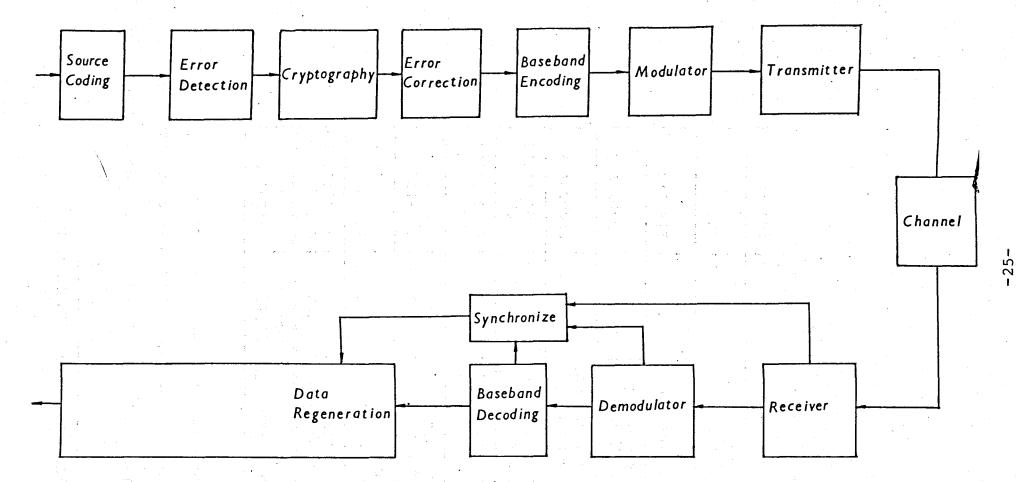

The position of cryptography in a communication system is shown in figure 1.5. Source coding must be done before the cryptosystem, since the cryptosystem hides the structure inherent in the English language. While error correction coding must be applied after the cryptosystem, because of the error propagation effects of good cryptosystem.

-24-

FIGURE 1.5 DIGITAL COMMUNICATION CHANNEL

# 1.6 PRACTICAL PUBLIC KEY CRYPTOSYSTEMS.

The PKC is more than a nice pedagogical idea. Since its inception many practical schemes have been proposed. A summary of some of these are given in table 1.2.

| n de la companya de l |          |                  |        |                           |

|-----------------------------------------------------------------------------------------------------------------|----------|------------------|--------|---------------------------|

| ! Cryptosystem<br>!                                                                                             | -        | Still<br>Secure? | !      | REFERENCES !              |

| ! DH key distribution<br>! scheme in GF(2 <sup>n</sup> )                                                        | !        | NO               | !<br>! | 117 !<br>sec. 1.6.1 !     |

| ! DH key distribution<br>! scheme in GF(p)                                                                      | !        | YES              | !      | 116 !<br>sec. 1.6.1 !     |

| ! RSA modular exponen.<br>! scheme in GF(2^n)                                                                   | . !<br>! | NO               | !<br>! | 121-122 !<br>sec. 1.6.3 ! |

| ! RSA modular exponen.<br>! scheme in R(n)                                                                      | . !<br>! | YES              | !      | 123 !<br>sec. 1.6.3 !     |

| <pre>! Binary knapsack ! (superinc. trapdoor)</pre>                                                             | · ! ·    | ?                | !      | 126 !<br>sec. 1.6.2 !     |

| <pre>! General knapsack<br/>! (superinc. trapdoor)</pre>                                                        | 1        | ?                | !      | Chapter 2 !               |

| General knapsack<br>(residue trapdoor)                                                                          | !        | ?                | !      | Chapter 3                 |

| ! Lu-Lee modular sum<br>! scheme                                                                                | !        | NO               | !      | 118-120 !                 |

| ! Shamir knapsack<br>! signature scheme                                                                         | !        | NO               | !      | 124                       |

| ! McEliece Goppa code<br>! scheme                                                                               | !<br>!   | YES              | !      | 125 !                     |

TABLE 1.2 PRACTICAL PKC'S

Most practical PKC's have proven weak under cryptanalysis. The security of the McEliece PKC is difficult to gauge, because it has received surprisingly little attention. However, it is still a valid possibility as no successful cryptanalysis has been published. The other three schemes which have proven resistant are described below.

The notations R and S will be used in the examples to represent the receiver and sender respectively.

1.6.1 DH key distribution scheme.

The first and simplest PKC was proposed by Diffie and Hellman in their original paper (Ref.116). The DH key distribution scheme is based on two reverse transformations: exponentiation and logarithms. Their original proposal was for arithmetic in GF(p), but later unwisely extended to GF(2^n).

Suppose a Sender (S) and Receiver (R) wish to establish a secret key. First S calculates  $x^c$ , sending x and  $x^c$  to R. R then calculates  $x^d$  and returns this to S. Both users can now compute  $x^cd$ , which they can use as their key. If x, c and d have been chosen randomly, a cryptanalyst is faced with a very hard problem. He must find either  $log(x^c)$  or  $log(x^d)$ , since he only possesses  $x^c$ ,  $x^d$ , x.

At the present time the best algorithm for finding logs depends on which field is used. For GF(2<sup>n</sup>), Coppersmith has

-27-

shown (Ref.117) how to break the scheme. However the method does not work in GF(p), where the security is much higher.

Example.

S: 3<sup>4</sup> mod 11 = 4

R: 3<sup>7</sup> mod 11 = 9

S: 9<sup>4</sup> mod 11 = 5

R: 4<sup>7</sup> mod 11 = 5

Giving a session key of 5.

1.6.2 MH trapdoor knapsack PKC.

Merkle and Hellman (Ref.126) intoduced a PKC based on the binary knapsack problem. This is a problem of the form: given a vector of n integers (the weight of each component) and the sum of a subset of these integers (the total weight), find which subset was used.

The hardest instances of the knapsack problem are known to be NP-complete. However for certain vectors (e.g. 1,2,4,8,16) the solution is trivial. The Merkle-Hellman scheme is based on using a superincreasing sequence, which has been disguised by modular multiplication (\*W mod Z).

Someone wishing to transmit an n bit message X, would transmit the sum of those components whose corresponding message bit were 1. The publisher of A could then use his secret key (W and Z), to transform this back into the easy superincreasing

knapsack problem.

The non-bijective mapping not only causes message expansion, but makes authentication difficult. Also the method requires a very large public key size. Despite this the scheme initially proved very popular. The reason was the simplicity of encoding and decoding, which meant it could run at the same speed as conventional cryptosystems.

Recently the original Merkle-Hellman scheme has been broken. Even stronger variants, such as the Graham-Shamir system (Ref.204) and the iterated knapsack method, have proven vulnerable. Despite this nobody has yet shown a general method of cracking all knapsack problems. So it is still feasable that a fast PKC, based on the knapsack problem, can be found.

Example.

R: A' = 8, 4, 2, 1

Z = 17, W = 11 --> 1/W = 14

A = 3, 10, 5, 11

S: Message = 1101

Ciphertext = 3 + 10 + 11 = 24 R: 24 \* 14 mod 17 = 13 --> 1101

1.6.3 RSA modular exponential PKC.

The most elegant and powerful PKC is that due to Rivest,

Shamir and Adleman (RSA). It uses the exponentiation function for both the encryption and decryption transformations (Ref.123): with arithmetic done in the ring R(n).

The two exponents e and d are chosen to be inverses modulo U(n) (see section 1.3.1). This means we can write:  $C = M^e \mod n$

$M = C^d \mod n$

In the RSA-PKC each user publishes a unique e and n, but keeps their d secret. It is believed that the best way to find d, and hence cryptanalyse a message, is to factor n. However, if n is chosen to be the product of two large (say 256 bits) safe primes (Ref.127), factoring is too computationally demanding. Therefore the RSA-PKC is still regarded as secure.

Example.

R: n = 5 \* 11 = 55 U(n) = (5-1).(11-1) = 40 e = 7, giving d = 23 S: Message = 1101 = 13 Ciphertext = 13^7 = 7 mod 55 R: Message = 7^23 = 13 mod 55

-30-

### 1.7 REFERENCES.

101 D.KAHN.

The codebreakers, the story of secret writing. MACMILLAN, 1967.

102 IEE WORKING PARTY.

Privacy and security in civil telecommunications. IEE, LONDON, SEP.1984.

103 J.A.GORDON.

Recent trends in cryptology.

ELEC. & POWER, VOL.26, NO.2, PP.162-165, FEB.1980.

104 W.DIFFIE & M.E.HELLMAN.

Privacy and authentication: An introduction to cryptography. PROC. IEEE, VOL.67, PP.397-427, MAR.1979.

105 G.J.SIMMONS.

Cryptography: the mathematics of secure communication. THE MATH. INTELLIGENCER, VOL.1, PP.233-246, JAN 1979.

106 M.E.HELLMAN.

An overview of public key cryptography. IEEE COMM. SOC. MAG., VOL.16, PP.24-32, NOV.1978.

#### BASIC TECHNIQUES.

107 D.E.DENNING.

Cryptography and data security.

ADDISON WESLEY, 1982.

108 M.WILLETT.

A tutorial on public key cryptography. COMPUTERS AND SECURITY, VOL.1, PP.72-79, 1982.

109 H.J.BEKER & F.PIPER.

Cipher systems: the protection of communications. Northwood books, London, 1982.

110 W.PRICE.

Developments in data security. NPL TECH. MEMO TTCC 14/83, OCT 1983.

111 W.L.PRICE.

Standards for data security, a status report. ONLINE CONFERENCE "NETWORKS 84", 1984.

112 F.AYRES, JR.

Theory and problems of modern algebra.

MCGRAW-HILL, 1965.

113 G.BRKHOFF & T.C.BARTEE.

Modern applied algebra.

MCGRAW-HILL, 1970.

114 D.E.KNUTH.

The art of computer programming: vol.2, seminumerical algorithms.

ADDISON-WESLEY, SECOND EDITION, 1981.

115 A.V.AHO, J.E.HOPCROFT, J.D.ULLMAN.

The design and analysis of computer algorithms. ADDISON-WESLEY, 1974.

116 W.DIFFIE & M.HELLMAN.

New directions in cryptography.

IEEE TRAN. INFO. THEORY, VOL.22, PP.644-654, NOV.1976.

117 D.COPPERSMITH.

Fast evaluation of logarithms in fields of characteristic two.

IEEE TRAN. INFO. THEORY, VOL.30, PP.587-594, JUL.1984.

118 S.C.LU & L.N.LEE.

A simple and effective public key cryptosystem.

COMSAT TECH. REV., VOL.9, NO.1, PP.15-24, 1979.

119 J.M.GOETHALS & C.COUVREUR.

A cryptanalytic attack on the Lu-Lee public key cryptosystem. PHILLIPS J. RES., VOL.35, PP.301-306, 1980.

#### BASIC TECHNIQUES.

120 M.J.KOCHANSKI.

Remarks on Lu and Lee's proposal for a public key cryptosystem.

CRYPTOLOGIA, VOL.4, NO.4, PP.204-212, 1980.

121 D.W.KRAVITZ & I.S.REED.

Extension of the RSA crypto-structure: a Galois approach. ELECTRONICS LETTERS, VOL.18, NO.6, PP.255-256, 18-MAR.1982.

122 P.DELSARTE & P.PIRET.

Comment on, extension of the RSA crypto-structure: a Galois approach.

ELECTRONICS LETTERS, VOL.18, NO.13, PP.582-583, 24-JUN.1982.

123 R.L.RIVEST, A.SHAMIR & L.ADLEMAN.

A method for obtaining digital signatures and public key cryptosystems.

COMM. OF ACM, VOL.21, NO.2, PP.120-126, FEB.1978.

124 A.M.ODLYZKO.

Cryptanalytic attacks on the multiplicative knapsack Cryptosystem and on Shamir's fast signature scheme.

IEEE TRAN. INFO. THEORY, VOL.30, PP.594-598, JUL.1984.

125 R.J.MCELIECE.

A public-key cryptosystim based on algebraic coding theory. JPL DSN PROG. REPORT 42-44, PP.114-116, JAN.-FEB.1978.

-34-

126 R.C.MERKLE & M.E.HELLMAN.

Hiding information and signatures in trapdoor knapsacks. IEEE TRAN. INFO. THEORY, VOL.24, PP.525-530, SEP.1978.

127 G.R.BLAKLEY & I.BOROSH.

Rivest-Shamir-Adleman public key cryptosystems do not always conceal messages.

COMP. & MATH. WITH APPLIC., VOL.5, PP.169-178, 1979.

CHAPTER

2

-36-

## 2.1 INTRODUCTION.

One of the most promising PKCs has been the Trapdoor Knapsack PKC (TK-PKC). The TK-PKC (see section 1.6.2) algorithm appeared to offer privacy and authentication (Ref.201) at high data rates (Ref.202). However it was apparent that, when compared with the RSA scheme (see section 1.6.3), this system had a number of drawbacks.

The most obvious problem with the TK-PKC is the size of the public key. At 80K bits per user, this would produce a very large public directory.

It was suggested in the original Merkle-Hellman paper, (Ref.126), that a possible means of reducing the key size was to use a non-binary knapsack problem. In this paper we shall build a model for this non binary TK-PKC and try to reduce the size of the public key.

Two other parameters are also considered in the design of this new system: the data expansion and security. The TK-PKC expands data by over 100%. This redundancy is unacceptable for many applications and we shall try to minimize it. More recent critisism of the TK-PKC has been on the security (Refs.202-206). In this chapter we shall just try to achieve a security equivalent to the original scheme. Improving security is subject of chapter 3.

-37-

| 2.2     | NOTATION.                                                  |

|---------|------------------------------------------------------------|

| a<br>i  | = i'th published knapsack component.                       |

| a´<br>i | = i'th secret knapsack component.                          |

| Е       | = ratio of (no. message bits : no. ciphertext bits).       |

| g       | = number of bits on x .<br>i,max                           |

| k       | = number of iterative modular multiplications.             |

| m<br>i  | = i'th modulus in iterative modular multiplications.       |

| n       | = number of knapsack components.                           |

| Ρ       | = number of bits in the public key.                        |

| Q       | = number of bits in the secret key.                        |

| S       | = hard knapsack problem: ciphertext.                       |

| sí      | = easy knapsack problem.                                   |

| t       | = number of bits in transmitted ciphertext.                |

| ť       | = number of bits in message.                               |

| v       | = number of random bits in the lsbs of each $\mathbf{x}$ . |

| w<br>i  | = i'th multiplier in iterative modular multiplications.    |

| x<br>i  | = g-bit message block.                                     |

| У       | = number of random bits in a'.                             |

| z       | = number of bits in each knapsack component.               |

# 2.3 THE GENERAL METHOD.

A general knapsack problem is one in which you are given a vector of n integers, together with an integer S equal to their weighted sum. The problem is to find which weights were used. The less general binary knapsack problem is one in which the weights are restricted to 0 or 1. In our case we shall let the weights be integers within the limits:

0 <= x < 2 g

Though this general knapsack problem is known to be NP-complete (Ref.207) there do exist subsets which are easy to solve. One such case is when the knapsack components a' are chosen such that:

$$(i-1)$$

a'>  $(\sum_{j=1}^{i} a') * x$

i  $(j=1 j)$  max ...2.1

Merkle and Hellman described a method of hiding this superincreasing sequence, using k iterations of modular multiplication. The resulting trapdoor knapsack is hard to solve without additional information. Each component is given by:

$$a = ((((a' * w) mod m) * ...) * w) mod m$$

i i l l l k k

where GCD (w, m) = 1

j j

$$2 < w < m$$

j j

...2.4

-39-

$$m > \sum_{i=1}^{n} a'$$

$$l \quad i=1 \quad i$$

$$g+l(n)+l$$

$$m > 2 \qquad * m$$

$$j \qquad j-l$$

where l(n) = 1 if n = 0, else the smallest integer greater than or equal to log n.

If all the knapsack components were published, anyone wishing to transmit a message x could calculate:

$$S = \sum_{i=1}^{n} x^* a \qquad \dots 2.5$$

The receiver could transform this hard knapsack problem into:

$$S' = \sum_{i=1}^{n} x * a'$$

where:

S' = ((((S \* w) mod m) \* ...) \* w) mod mk k l l l

which can easily be deciphered (Ref.126).

# 2.4 EFFECT OF PARAMETER SELECTION.

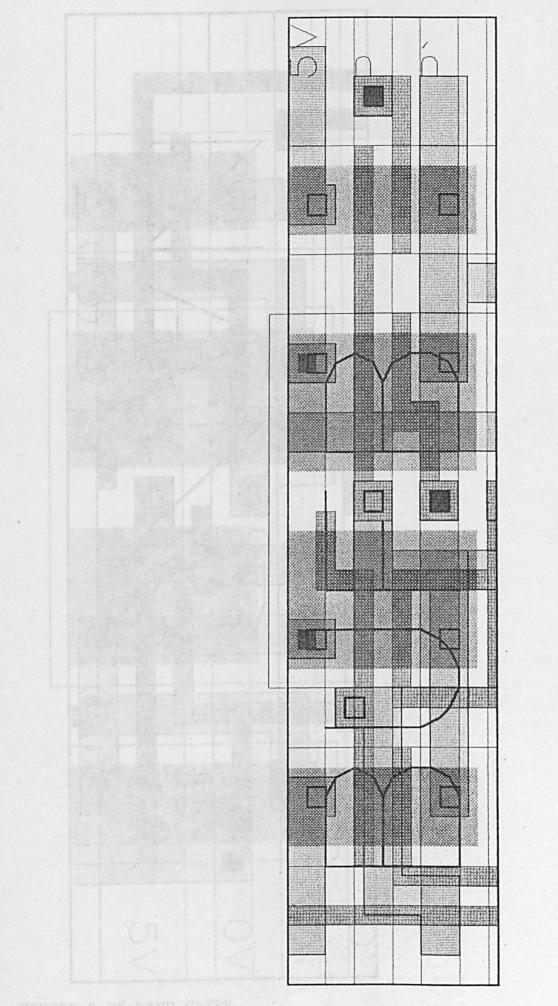

The superincreasing knapsack components are defined according to the structure shown in figure 2.1. Thus the third component would have its most significant bit set to 1 followed by 2g-1 0's and finally y random bits (R3). We know the number of bits (z) in each component is given by:

-40-

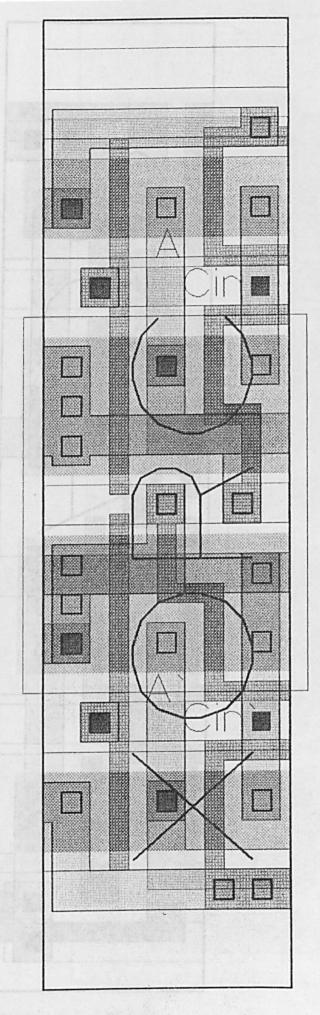

(k-1)(1(n)+q)ng !<---->!<l(n)+g ! g g g У !<---->!<---->! !!! 1 1 a'l !00... ! 1 1 1 ! ..00! R1 a'2 !00... ! ! ...00! ! ! ...00! ! ..00!10...00! ! ! ..00! R2 a'3 !00... ! ..00! R3 I ! . 1 1 1 1 1 ! . . · ] !. 1 1 a´n !00...! ..00! ! ! ..00!100.. RN 100....!! ...00!1! RI ml !00... !1! m2 RII 1. 1.1 mk !1! Rk FIGURE 2.1 COMPONENT SELECTION IN A GENERAL TK-PKC = 1(m)z ) k,max From figure 2.1, = y + g.n + (k-1).(g + 1(n))z ...2.6 From equation 2.5: S = n \* ((2 - 1), (2 - 1))max = n.(2 - 2 - 2 + 1)log n But n = 2 . If z >> g. then the number of bits transmitted: t = z + q + l(n)Substituting for z from equation 4, we obtain: t = y + g.n + k.(q + l(n))...2.7 But the number of actual message bits transmitted: t' = g.n ...2.8

Therefore the ratio of message bits to ciphertext bits is: = 1 : 1 + k/n + ((1/n).g).(y + k.1(n))Ε ...2.9 The number of bits in the secret key is given by: Q = k.((no. bits in w) + (no. bits in m))= 2.k.zTherefore from equation 2.6: = 2.k.(y + g.n + (k - 1).(g + 1(n)))0 ...2.10 The number of bits in the public key: P = n.zTherefore from equation 2.6: Ρ = n.(y + q.n + (k - 1).(g + 1(n)))...2.11 The above results are summarized in table 1. ! ORDER OF MAGNITUDE !------1 ! VAR. ! n ! g ! y ! k E ! l/n ! l/g ! y ! k 1 ! 1 . \_\_\_\_!\_\_\_\_\_\_ ! ! ! ! 2! 1 Q ! n ! g ! y ! k ! 1 ! ! ! ! 1

P!n!g!y!

I.

2.5 LIMITATIONS ON PARAMETER SELECTION.

! 2 !

1

The choice of parameters is limited by security

k !

1

1

\_\_\_\_\_1

1 1

1

TABLE 1 EFFECT OF PARAMETERS ON EFFICIENCY AND KEY SIZE.

considerations. There are two possible attacks on the general TK-PKC.

2.5.1 Breaking the trapdoor.

To achieve equivalent security to the Merkle-Hellman TK-PKC the superincreasing knapsack components must be well hidden. The two parameters which affect this are k and y. For a given n and g we set the following limitations:

y \* k > 200 ...2.12 k > 1 ...2.13

2.5.2 Breaking the knapsack problem.

By expanding the message into its binary form it is possible to turn a general knapsack into a binary one. That is if:

Then we can write a general knapsack problem as:

$$S = \sum_{i=1}^{n} \sum_{j=0}^{g-1} (a) (x)$$

where:

This is a binary knapsack problem. In order to present a large equivalent binary knapsack problem we set:

-43-

n \* g > 200

...2.14

This limit is not sufficient, since not all message bits are equally well hidden. For example, the least significant bit (lsb) is only determined by the n lsbs of each message component. To overcome this weakness the general knapsack must employ a number of random bits in the lsbs of each message vector. If v is the number of random bits, then we can approximately compensate for the effect of a small n (provided n > 2) with the following limitation:

$$n * \frac{(v+1)}{2} > 128$$

...2.15

Let E' be the efficiency with v random bits added to each message component. Then it can be shown that:

$$E' = E + -\frac{v}{g}$$

...2.16

In the past few years there have been rapid advances in solving the knapsack problem. Though these attacks have been on the binary version (g = 1), the techniques can be extended to cover the general knapsack problem.

The technique (Ref.209) are based on forming a lattice of rank n appear particularly attractive. If:

-44-

Density =

$$\frac{n}{2}$$

$\frac{1}{2}$   $\frac{1}{2}$

then a binary knapsack problem can be broken. However for the general knapsack problem, with the additional restraint of equation 2.15, finding a suitable lattice is more difficult. In this case a better measure is to say:

...2.17

Density =  $\frac{n \cdot (g - v)}{h + 1} = \frac{1}{\log n}$

2.6 A BINARY TK-PKC.

The Merkle-Hellman method is a general TK-PKC with parameters:

n = 200, g = 1, y = 200, k=2.

With these parameters we obtain (equations 8.12-8.15):

E = 2.09, Q =1628 bits , P = 81400 bits.

2.7 A NON BINARY TK-PKC.

Using the assumptions of section 2.6 we can choose an alternative set of parameters. The additional guides used to choose them are:

a) Only the receiver stores Q, so its size is not critical.b) All users must either store or be transmitted P, so its size should be minimized.

-45-

c) Data expansion is a waste of resources, therefore minimize E.

Combining these observations with those of table 2.1, an alternative set of parameters are chosen: n = 7, g = 32, y = 100, k = 2. With this new set of parameters we find: E = 1.76, Q = 1436 bits, P = 2513 bits.

In order to compensate for the effect on security of the small n (see section 2.5.2) we must have approximately 5 random bits (v) in the lsbs of each message (equation 2.15). This reduces the efficiency (equation 2.16) to:

E' = 1.92

## 2.8 CONCLUSION.

In this chapter we have demonstrated a non-binary TK-PKC with equivalent security to the Merkle-Hellman method. It has the advantage that the resulting public directory would be 35 times smaller. It also has less message expansion.

Recent improvements in cracking the knapsack problem (Refs.208-209) have been dramatic. These polynomial time solutions have been successful against the binary TK-PKC. As the general system is no more secure than the binary problem, this puts into question the use of this type of knapsack in cryptography.

-46-

A particular weakness with the TK-PKC is the trapdoor information. In the next chapter we shall describe a system not based on superincreasing sequences.

2.9 REFERENCES.

201 P.SCHOBI & J.L.MASSEY.

Fast authentication in a trapdoor-knapsack public key cryptosystem.

IEEE SYMP. ON INFO. THEORY, LES ARCS, FRANCE, JUN.1982.

202 P.S.HENRY.

Fast decryption algorithm for the knapsack cryptographic problem.

BELL SYSTEMS TECH. J., VOL.60, PP.767-773, MAY-JUN.1981.

203 T.HERLESTAM.

Critical remarks on some public key cryptosystems.

BIT, VOL.18, PP.493-496, 1978.

204 A.SHAMIR & R.E.ZIPPEL.

On the security of the Merkle-Hellman cryptographic scheme. IEEE T. ON INFO THEORY, VOL.26, PP.339-340, MAY 1980.

205 Y.DESMEDT, J.VANDEWALLE & R.GOVAERTS.

A critical analysis of the security of knapsack public key cryptosystems.

IEEE T. ON INFO THEORY, VOL.30, PP.601-611, JUL.1984.

206 I.INGEMARSSON.

A new algorithm for the solution of the knapsack problem. IEEE SYMP. ON INFO. THEORY, LES ARCS, FRANCE, JUN.1982.

207 E.HOROWITZ & S.SAHNI.

Computing partitions with applications to the knapsack problem.

J. OF ACM, VOL.21, PP.277-292, APR.1974.

208 A.SHAMIR.

A polynomial-time algorithm for breaking the basic Merkle-Hellman cryptosystem.

IEEE T. ON INFO THEORY, VOL.30, PP.699-704, SEP.1984.

209 E.F.BRICKELL.

Solving low density knapsacks in polynomial time. IEEE SYMP. ON INFO. THEORY, ST.JOVITE, CANADA, SEP.1983.

-48-

CHAPTER

3

## 3.1 INTRODUCTION.

This chapter presents a new trapdoor knapsack public key cryptosystem (TK-PKC). The encryption equation is based on the general modular knapsack equation (see chapter 2), but unlike the Merkle-Hellman scheme the knapsack components are not derived from a superincreasing sequence.

The trapdoor is based on being able to transform between the radix and modular representations of the components, via the Chinese Remainder Theorem (Ref.115). The system bears a resemblance to the Lu-Lee system (Ref.118), but whereas their cryptosystem is linear and has been shown to be insecure (Refs.119-120), ours is based on the general modular knapsack equation, which to date has not been generally broken.

The new TK-PKC has a number of advantages over the original system other than security. Firstly, the public key size is reduced from 80K bits to 14K bits. Secondly, the redundancy is reduced from over 100% to around 25%. Compared with the RSA scheme (see section 1.6.3) its main advantage is speed. Typically, knapsack schemes are capable of throughput speeds which are several orders of magnitude faster than the RSA scheme.

-50-

3.2 NOTATION. = i'th published knapsack component. a . a´ = i'th secret knapsack component. i = published knapsack vector = (a, a, ..., a). А = secret knapsack vector =  $(a', a', \ldots, a')$ . Aʻ = ratio of (no. message bits : no. ciphertext bits). Ε = number of bits on x g i.ma h+1 = minimum number of bits in any p. = number of knapsack components. n = a.set of n distinct primes =  $(p, p, \dots, p)$ . Ρ p \_i = h+l bit prime number.  $= \prod_{i=1}^{n} p.$ р ΡK = number of bits in the public key. = maximum number of bits in  $\left(\sum_{i=1}^{n} a'_{i}\right)$ . r S = hard knapsack problem: ciphertext. s′ = easy knapsack problem. = number of random bits in the lsbs of each x . V W = a secret modular multiplier, relatively prime to p. = n \* g bit message vector =  $(x, x, \dots, x)$ . Х x = g-bit message block. i

-51-

## 3.3 THE NEW TRAPDOOR.

The general modular knapsack problem is given by:

$S = \sum_{i=1}^{n} a \cdot x \mod p \qquad \dots 3.1$

When used for cryptography, the a's are the n published knapsack components, p is a published modulus, and the x's are the message bits. In the binary knapsack the x's are 0 or 1, but in the general knapsack they are g bit numbers. The subset sum S is the cryptogram, which only the legitimate user is able to unwind back to the original x's.

$p = \prod_{i=1}^{n} p$   $i=1 \quad i$ If a = a mod p  $j \quad j \quad i$

is the residue of the j'th knapsack component modulo the i'th prime. Then, by the Chinese Remainder Theorem:

(1) (2) (n) a <----> a , a , ... , a j j j j j

is a bijective mapping. That is, the transformation is one-to-one for all a's between 1 and p-1. Thus if the factorization of p is kept secret, then only the legitimate user will be able to transform the radix representation of the knapsack components into their modular representation. This forms our secret new

-52-

trapdoor. Let us now choose a set of n knapsack components and express them in both radix and modular form:

$$a' <----> a' , a' , a' , \dots , a' (n)$$

$$a' <----> a' , a' , \dots , a' (n)$$

$$a' <----> a' , a' , \dots , a' (n)$$

$$a' <----> a' , a' , \dots , a' (n)$$

$$a' <----> a' , a' , \dots , a' (n)$$

Let us then disguise the trapdoor by forming a new set of knapsack components, via the modular multiplication:

...3.2

$$a = a' \cdot w \mod p$$

...3.3

where w and p are relatively prime. Under this condition we know there exists an inverse (see section 1.3.1) transformation:

We now publish p, and the modified knapsack components (A) in radix form. This is the public key. The factorization of p and the integer w are kept secret, and hence so is the modular representation of the components (A').

that is, the primes are at least h+1 bit numbers.

that is, the message blocks are g bit numbers.

And let

$$(n (i))$$

r

$(\sum_{j=1}^{r} a') < 2$  ...3.6

$(j=1 j) max$

that is, the columns of A' sum to an r bit number.

In order to ensure that the encryption equation has a unique decryption, we must ensure that the message to ciphertext transformation  $X \rightarrow S$  is injective. To guarantee this we must have:

h >= r + g ...3.7

This also ensures that modular multiplication is equivalent to

matrix multiplication:

| (1)<br>(s´,,s´) | = (x , , x<br>1     | ( (1) (2)<br>) (a´ ,a´ ,<br>n (1 1<br>( | (n))<br>, a')<br>1)                   |

|-----------------|---------------------|-----------------------------------------|---------------------------------------|

|                 |                     | (.                                      | · · · · · · · · · · · · · · · · · · · |

|                 | a statistica second | ( .                                     | )                                     |

|                 |                     | ( (1) (2)<br>(a´ ,a´ ,<br>( n n         | (n))<br>, a´)<br>n)                   |

i.e  $S' = X \cdot A'$

If the matrix (A') is non-singular, then:

$$-1$$

X = S'. A' ...3.8

The cryptosystem then operates as follows. A user wishing to send us a message forms the ciphertext:

-54-

From equation 3.1 we compute:

-1S' = S. w mod p

Then, through our known factorization of p, we can tranform:

s' <----> (s' , s' , ... , s' )

We then apply X = S'. A' and hence recover the message.

The cryptanalyst must either break the factorization of p, attack the trapdoor in some other way (see section 3.5), or solve the general knapsack problem (see section 2.5.2).

# 3.4 A SMALL EXAMPLE.

In order to help understand the ideas of the last section, a small example is now presented. The example is of Course too small for security.

Let n=3 and define P=(37,41,43), hence p=65231, and h=5 (equation 3.4). Choose g=2, that is, the message components are two bit numbers. This dictates that r=3 via equation 3.7 (h>=3+2). Choose n=3 knapsack components which satisfy eqation 3.6, that is, the columns of A' add to less than eight, and express in both modular and radix form:

-55-

$$a' = (3, 1, 1) < ----> 125174$$

$$a' = (1, 5, 3) < ----> 151664$$

$$a' = (2, 1, 2) < ----> 122509$$

Now choose w=6553 which is relatively prime to p=65231. Perform the modular multiplication of equation 3.3, and publish the resulting knapsack components:

a = 506281 = 59907

a = 3560

and the modulus p = 65231.

Compute the invese w = 6553 (see section 1.3.1), and invert A':

$A^{-1} = (1/16) (+7, -1, -2) (+4, +4, -8) (+4, +4, -8) (-9, -1, +14)$

To transmit a six bit message X=(1,2,3) a user computes the ciphertext:

S = (1.50628) + (2.59907) + (3.3560)

= 181122

$= 50660 \mod 65231$

Using the secret inverse w the receiver computes:

-1

$S' = 50660.2618 \mod 65231$

$= 13257 \mod 65231$

-56-

Using the secret factors of p, the receiver transforms this into modular form:

S' = (11, 14, 13) < ----> 13257

From equation 3.8, the receiver computes:

16.x = (11, 14, 13) (+7, -1, -2) (+4, +4, -8) (+4, +4, -8) (+6, -9, -1, +14)

giving X = (1, 2, 3) as transmitted.

3.5 PRACTICAL CONSTRAINTS.

The choice of parameters (n, r, g and h) is limited by security considerations. Their are two possible attacks on security that we shall consider.

3.5.1 Breaking the general knapsack problem.

The general knapsack problem is identical with that of the last chapter. Therefore we must have the same limits (see section 2.5.2). If v is the number of random bits in the lsbs of each x, then:

n \* g > 200

...3.9

...3.10

n \* (v+1) > 256

3.5.2 Breaking the trapdoor.

From equation 3.3 we can write:

$a - a' \cdot w = 0 \mod p$ ...3.11  $a - a' \cdot w = 0 \mod p$ ...3.12 We can now calculate (eqn.3.11 and eqn.3.12):  $a \cdot a' - a \cdot a' = 0 \mod p$ j l l j writing this in modular form we get: (i)  $a \cdot a' - a \cdot a' = 0 \mod p$   $j \ l \ j \ i$ ...3.13 (i) If the number of combinations of a were too small eqn. 3.13 could be used to break the new TK-PKC. Therefore we set a limit: r >= 63...3.14 In order to stop a factorization attack, we must set: h >= 255 ...3.15 3.6 A SECURE TK-PKC. The efficiency of the cryptosystem is given by: h + 1 + vE = 1 : ----if we assume all primes are exactly h + 1 bit numbers. From equation 3.7 we get: g + r + 1 + vE = 1 : -----...3.16

Therefore to minimize E, r and v should be kept small.

The size of the public key (PK) is given by:

...3.17

### PK = n.(n + 1).(h + 1)

In order to reduce this, n should be kept small.

From the above arguments and the security restraints of section 3.5, we end up with the following parameters: n = 7, r = 63, h = 255, g = 192, v = 5. Which from equations 3.16 and 3.17 give: E = 1 : 1.36, PK = 14336 bits.

3.7 CONCLUSION.

In this chapter we have presented a new public key cryptosystem based on the general modular knapsack problem. Its security is not based on disguising a superincreasing sequence, but on the difficulty of factoring a number with seven 256 bit prime factors, and on a knapsack problem with a typical efficiency of 1:1.36 and block size of 1736 bits.

The knapsack nature of the system ensures that fast encryption and decryption are possible. In addition the size of the public key, which is typically 14K bits, is not excessive.

It may be possible to attack the trapdoor information more directly, but we can see no productive method of doing this. The only successful attacks on dense trapdoor-knapsacks to date have been on the security of the superincreasing sequence. Our method does not require this. However, it may turn out that all injective trapdoor knapsacks are solvable in polynomial time, in which case all such schemes are useless for cryptography.

CHAPTER

## 4.1 INTRODUCTION.

Using a PKC any two users of a network can communicate securely, without the problem of key distribution (see section 1.4). This overcomes one of the big drawbacks to the use of cryptography. However, there are many cases where the same message needs to be sent to a group of users. The application of cryptography would then severely degrade the network.

In this paper we consider the problem of how to securely set up a broadcast transmission in an electronic network environment. Such networks include broadcast satellite and packet switched digital data services. We assume that any user may take the role of broadcaster, and that the broadcaster wishes to send an identical message to any subset of other users.

# 4.2 MULTIDESTINATION ADDRESSING.

Through his paper in 1978 (Ref.401), J.McQuillan intoduced three enhanced addressing modes:

Logical addressing, where a permanently assigned address can denote one or more physical address.

2. Broadcasting, where the message is addressed to all subscribers.

3. Group addressing, in which the message carries a list of addresses.

These three modes were shown to provide more flexibility, greater

-61-

reliability and a reduction in network traffic.

The application of these enhanced addressing modes to cryptogaphic networks is far from straight forward. The problem can be overcome by distributing a session key. But this does not necessarily reduce the order of magnitude of the problem. It would be particularly inefficient for a large number of receivers or a small message.

An alternative solution is to trade complexity in terms of the number of keys in the system rather than the distribution time. In this case however there is an explosive growth in the number of keys required.

For a network with n users, a message intended for a subset k of these would require either:

a) O(k) transmissions.

b) O(n!) keys per user.

If the application of cryptography is not to severely degrade system performance, a more efficient solution must be found.

# 4.3 EXPLOITING NETWORK STRUCTURE.

If the network has the form of a ring, such as in a local area network, we can consider the following distribution method. The broadcaster enciphers the session key and a list of station addresses under the public key of the first receiver, in

-62-

say a clockwise direction. This receiver deciphers the information, and then re-enciphers under the public key of the next receiver on the list.

The information is thus passed from user to user round the ring, with only the intended subset of users able to decipher the session key and addresses. Additionally, each of the intended receivers can 'sign' the re-enciphered information, using the signature property of a PKC, before passing the packet on. After the packet has been round the ring, the broadcaster can check to ensure no user has missed the message: either intentionally or because of error.

## 4.4 EXPLOITING SECURITY STRUCTURE.

An alternative method of exploiting structure exists if the network of users have a fixed security structure. For example, if the users form a layered hierarchical structure then security can be arranged in layers, with a pair of keys for each level in the hierarchy. Thus the level 1 key would only allow level 1 users to decipher a message. The level 2 key would allow both level 2 and level 1 users to decipher, and so forth. Any particular level therefore possesses the keys to its own level and those below it.

With the above arrangement the maximum number of keys would be O(n). If this is too large, a trade-off of the number of

-63-

keys for the number of transmissions is possible. For example with O(logn) keys only O(logn) transmissions are needed.

## 4.5 A BROADCAST CRYPTOSYSTEM.

Each user's public key defines a one to one mapping between a particular message and ciphertext. The secret decryption key defines the inverse mapping (see section 1.3). It is possible that two keys might define the same mapping, for a particular ciphertext. That is, the same ciphertext will produce the same message under a different key. This would allow the broadcast of a session key in a single transmission.

There are, however, a number of reasons why the above scheme is not practical as it stands. Firstly, no such session key may exist between a group of users. Secondly, if such a key exists, there might be too few for security. Finally, there is the problem of how to find these session keys.

# 4.5.1 Use of message redundancy.

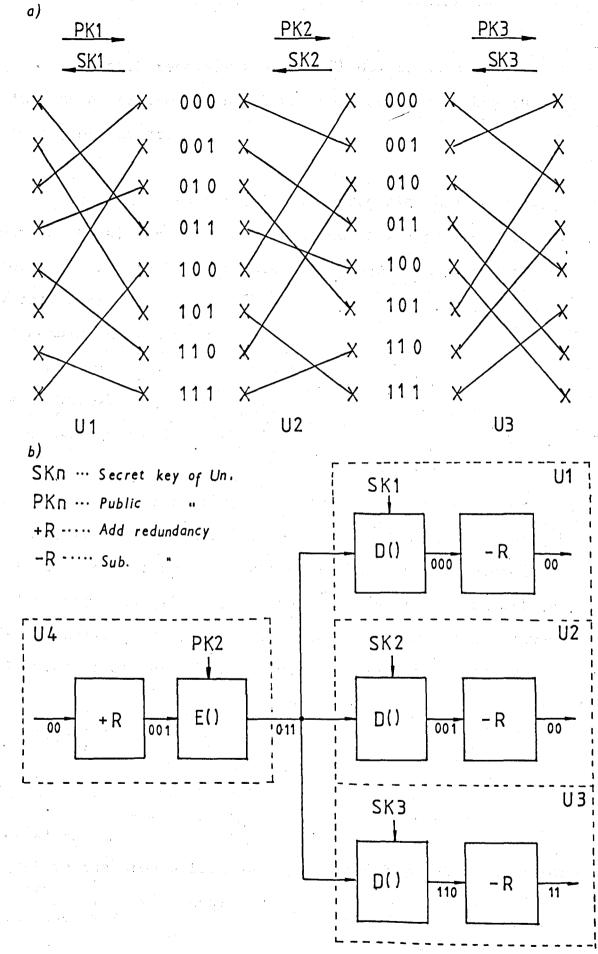

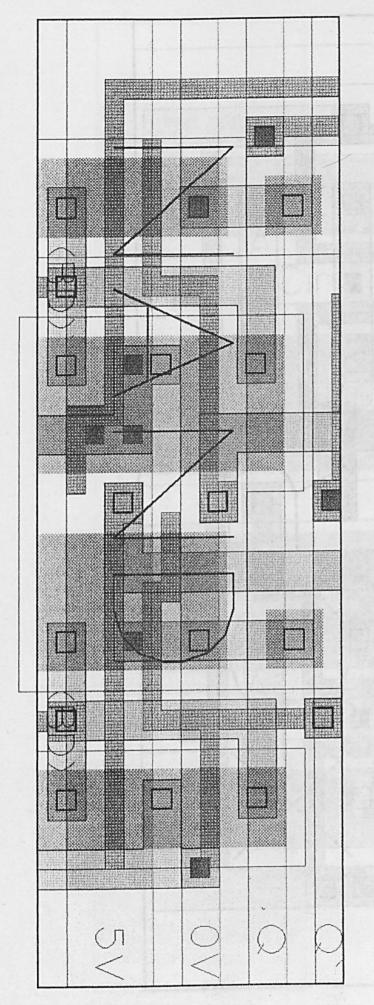

A given ciphertext does not have to decipher to exactly the same message for each intended receiver, but rather the subset of bits that forms the session key does. As an small, example consider the problem of transmitting a 2-bit session key to two of three receivers.

-64-

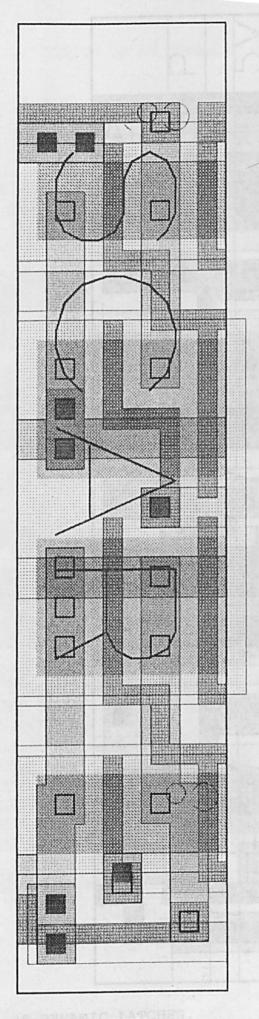

FIGURE 4.1 SESSION KEY BROADCAST TO 2 OF 3 RECEVERS.

If each receiver mapping (Ul-U3) is as shown in figure 4.1a, then figure 4.1b shows how the session key (00) can be securely broadcast.

Though it is intuitively reasonable that there are more session keys, it is important to know approximately how many there are. This will allow us to gauge the security of the system. Let:

m = number of bits in message.

c = number of bits in ciphertext.

r = number of redundant bits.

k = number of receivers.

When enciphering an (m-r) bit session key, there will be 2<sup>r</sup> different ciphertexts for a given public key. The probability that one of these ciphertexts would be produced under another public key is: 2<sup>(r-c)</sup>. For k users the probability is: 2<sup>(r-c)</sup>(k-l). The probability that none of the 2<sup>r</sup> ciphertexts will yield a suitable session key, P(fail), is given by:

$$P(fail) = \begin{pmatrix} (r-c).(k-1) \\ 1 - 2 \end{pmatrix}$$

As a first order approximation:

r + (r-c).(k-1)P(fail) = 1 - 2

Therefore the probability of one session key being suitable:

c + k.(r-c)P(success) = 2

Of the 2<sup>(m-r)</sup> possible session keys, let Q be the

number that are correctly deciphered by all k receivers. It follows that:

(m-r) Q = 2 \* P(success) . m + c.(l-k) + r.(k-1) Q = 2Let  $Q = 2^b$ , then:

If we assume a bijective mapping (m = c) then:

...4.1

For security it is important to have a sufficiently large session key and choice of session keys. If we say both must have a selection of at least 2<sup>v</sup>, then: b = m - r = v ...4.2 Substituting into equation 4.1 we obtain: (m -v).(k-1) = v + m.(k-2)Therefore in order to have a practical cryptosystem: m = v.k ...4.3

Equation 4.3 tells us that for a given message size (m), the number of receivers (k) who can obtain a session key in one broadcast is inversely proportional to the security (v). That is we have a degradeable cryptosystem, where it is possible to trade security with the number of receivers.

#### KEY EXCHANGE IN A BROADCAST ENVIRONMENT.

4.5.2 A practical broadcast cryptosystem.

Consider how the ideas of the last section can be applied to a trapdoor knapsack PKC (see section 1.6.2). Let Cl and C2 be the ciphertexts formed by two users keys:

$$Cl = \sum_{j=1}^{m} a * x$$

$$j=1 \quad j, 1 \quad j, 1$$

$$C2 = \sum_{j=1}^{m} a * x$$

$$j=1 \quad j, 2 \quad j, 2$$

a = j th knapsack component of user k.

j,k

We require Cl = C2, and the first (m-r) bits of each message to be the same. Therefore:

$$\sum_{j=1}^{m-r} (a - a) \cdot x + \sum_{j=m-r+1}^{m} a \cdot x + \sum_{j=m-r+1}^{m} a \cdot x = 0$$

j=1 j,1 j,2 j,1 j=m-r+1 j,1 j,1 j=m-r+1 j,2 j,2

. 4

or

2m-r = 0 a.x where a = a= a - a j,l j,2 to j = m-r for j = 1j for j = m-r+1 to j = m= a j,1 for j = m+1to j = 2m-r= a j-r,1 x j for j = 1and to j = m = x j,1 = x for j = m+1 to j = 2m-rj-r,1

-68-

#### KEY EXCHANGE IN A BROADCAST ENVIRONMENT.

To find a solution to equation 4.4 does not seem practical, since it would be even more difficult than breaking the knapsack cryptosystem. However it is possible to exploit the fact that there is not just one solution, but approximately 2°b.

Consider what happens if we combine two vectors. That is, we force two message components to be the same: either both 1 or both 0. When we do this the number of knapsack components is reduced by one, but the number of probable solutions is reduced by half. So after f combinations, there will be 2m-r-f components and approximately 2<sup>(b/f)</sup> solutions.

To help explain the principle, consider a small example. We wish to distribute a 3-bit key to 2 users whose public keys consist of 8 knapsack vectors:

a = (123, 92, 233, 61, 11, 188, 103, 134)

b = (132, 210, 177, 70, 201, 107, 88, 54)

We want the first three message bits to be the same. This forces us to combine the first three components of the two receivers. Combining an extra five terms we get 8 new knapsack components:

c = a - b = -09 1 1 1 c = a - b + a = +16 2 2 2 8 c = a - b - b = +02 3 3 3 8 = +61 c = a = +61

| с<br>5 | = | 5       | + | a<br>6 | - | b<br>5 | = | -02 |

|--------|---|---------|---|--------|---|--------|---|-----|

| с<br>6 | = | -b<br>7 | x |        |   |        | = | -88 |

| с<br>7 | - | -b<br>4 |   |        |   |        | = | -50 |

| с<br>8 | = | a<br>7  | _ | b<br>6 |   |        | = | -04 |

It is now possible to find components that satisfy equation 4.4: 61 + 02 - 50 - 09 - 04 = 0

Therefore all terms in new components 1, 3, 4, 7, 8 must be 1. That is:

ax = (1,0,1,1,0,0,1,0)bx = (1,0,1,1,0,1,0,1)

The ciphertext which results when either of these vectors is enciphered is 520. Both receivers will obtain the session key (1,0,1).

In a practical system we would choose f=b, giving a 50% chance of solution. Clearly the algorithm used to select the combinations should be random. If it is not the process could be duplicated by a cryptanalyst.

4.6 CONCLUSION.

It has been shown that in a packet switched network, considerable savings in transmission time, that is, packet hops, can be achieved using multi-addressed packets. In this chapter we have considered the problem of secure communication of such a

-70-

#### KEY EXCHANGE IN A BROADCAST ENVIRONMENT.

broadcast.

Three possible solutions were put forward, which are not mutually exclusive. Taking advantage of the network structure and security hierarchy were two of the schemes. However, these can only be applied in certain cases.

A more general solution to the broadcast problem was also put forward. It uses redundancy between the messagetext and ciphertext. The method effectively trades security with redundancy, number of users, and transmission time.

Finally we present a practical broadcast cryptosysem based on the knapsack PKC. It is applicable to any knapsack cryptosystem, including our own given in chapter 3.

### 4.7 REFERENCE.

#### 401 J.M.MCQUILLAN.

Enhanced message addressing capabilities for computer networks.

PROC. IEEE, VOL.66, NO.11, PP.1517-1527, NOV.1978.

-71-

CHAPTER

5

-72-

### 5.1 INTRODUCTION.

Books, films, television, records and computer software can all be stored and distributed in digital form. Electronic publishing, where information is stored in data banks and distributed over a convenient communication channel, offers many advantages over traditional methods of distribution. However if it is to replace other means of publishing, it is necessary to provide a means of rewarding the Author, Producer, Musician or Programmer.

Copyright is traditionally used to protect the publisher from the pirate. In this chapter methods of enforcing the copyright law will be considered. In particular the application of a PKC to the problem.

### 5.2 ELECTRONIC PUBLISHING.

Writing programs for personal computers is now a big business, approaching the level of more traditional published information: such as books, television and films. In the next ten years an increasing proportion of this information will be distributed in digital form. This offers many advantages:

Ease of distribution - e.g. over telephone lines.

2. Less redundancy - The size of a market for books is often unpredictable. But since copies can be quickly and cheaply made, unnecessary copies need not be produced.

3. Fast update - The lag between supply and demand can be broken.

Electronic publishing does have some disadvantages. Some people might like the feel of vinyl or not like reading from a screen. But though many of these ergonomic problems can be overcome, one major problem remains: how to stop people making illegal copies.

In order to make publishing worthwhile, it must be possible to reward those responsible for developing the product. However information stored in digital form is very much easier to copy, making copying more financially rewarding.

# 5.3 COPYRIGHT AND CRYPTOGRAPHY.

Copyright is used to give the sole legal right to print, publish, perform, film or record a literary, artistic or musical work (Ref.501). This legal deterrent could easily be extended to cover the newer forms of information, such as computer software. However the ease and cheapness with which electronic information can be copied, suggest that better methods of circumventing the pirate are needed. In the field of computer software, some estimates say as few as 1 in 10 copies may be legally obtained.

Cryptography has been used for centuries to secure communications over a public link. But because the receiver cannot be relied upon to keep the information secure, this

-74-

technique cannot be directly applied to copyright protection.

There have been a number of papers on how cryptography can be applied to protect software (Refs.502-504). However, these methods are not generally applicable to the wider field of copyright protection.

## 5.4 SOFTWARE PROTECTION.

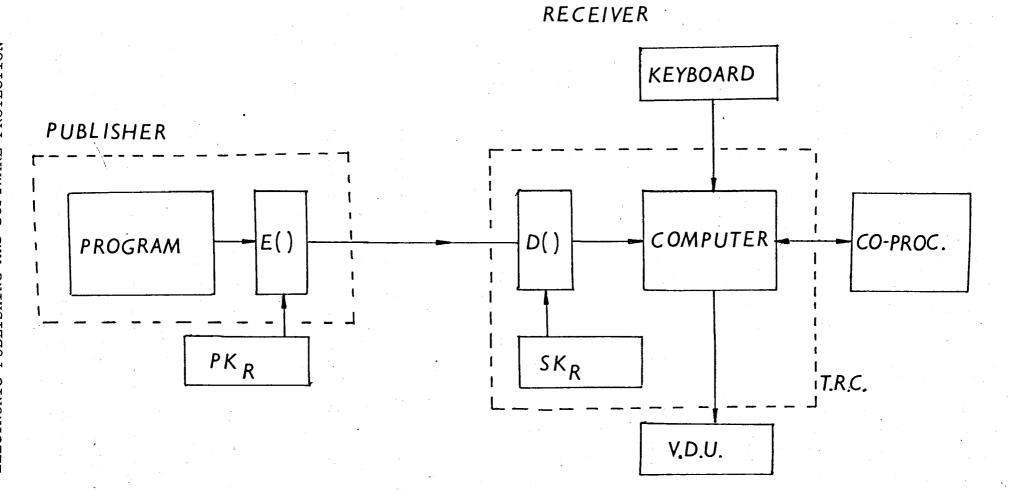

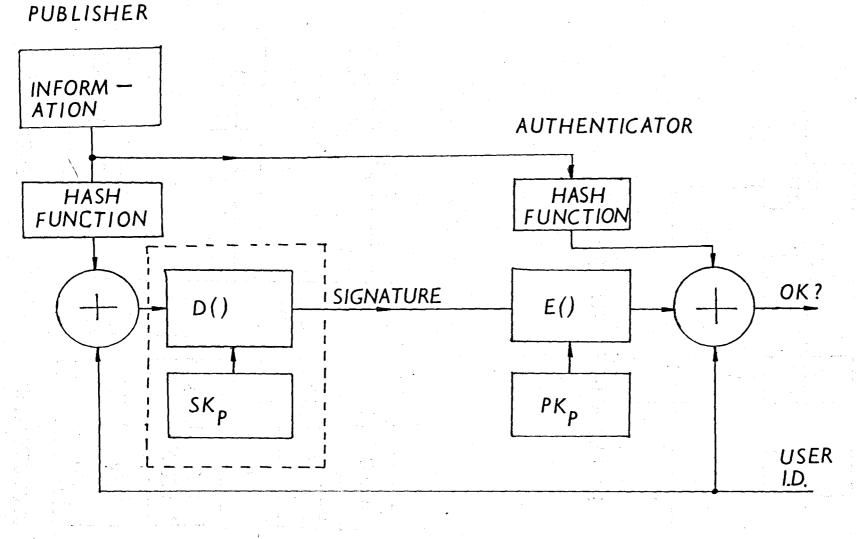

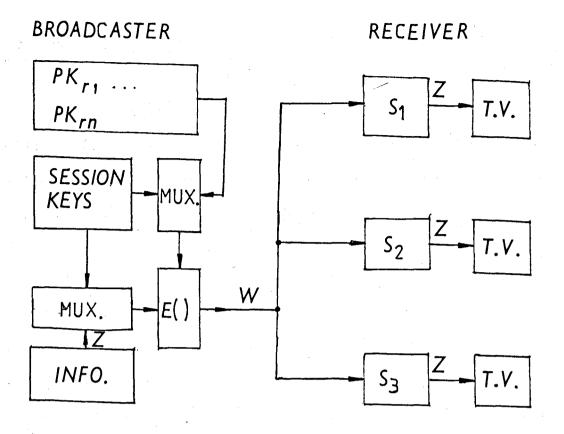

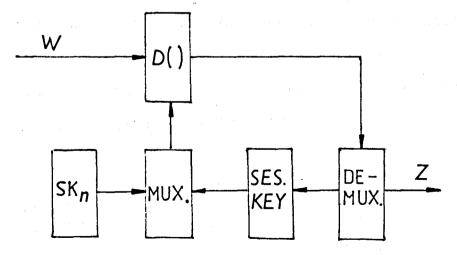

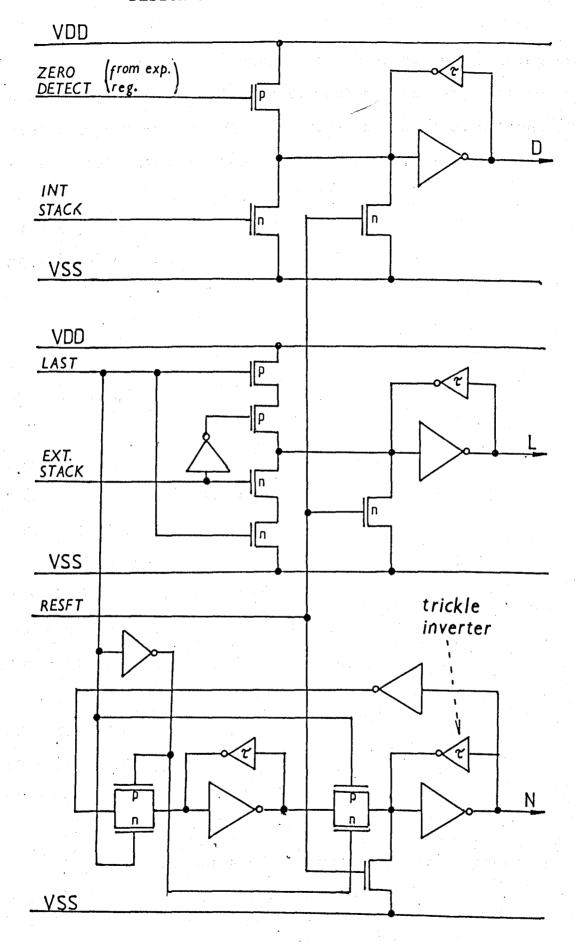

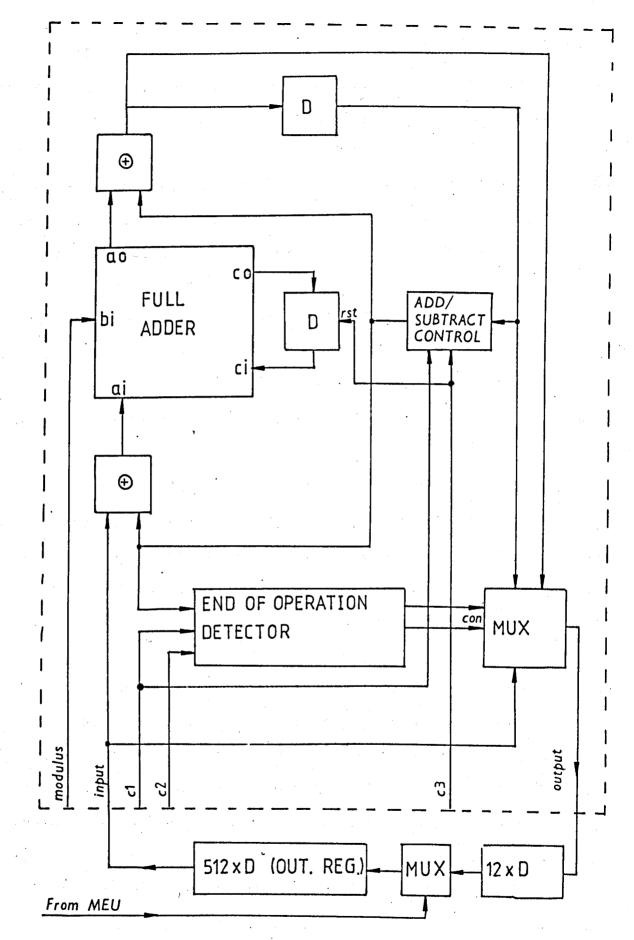

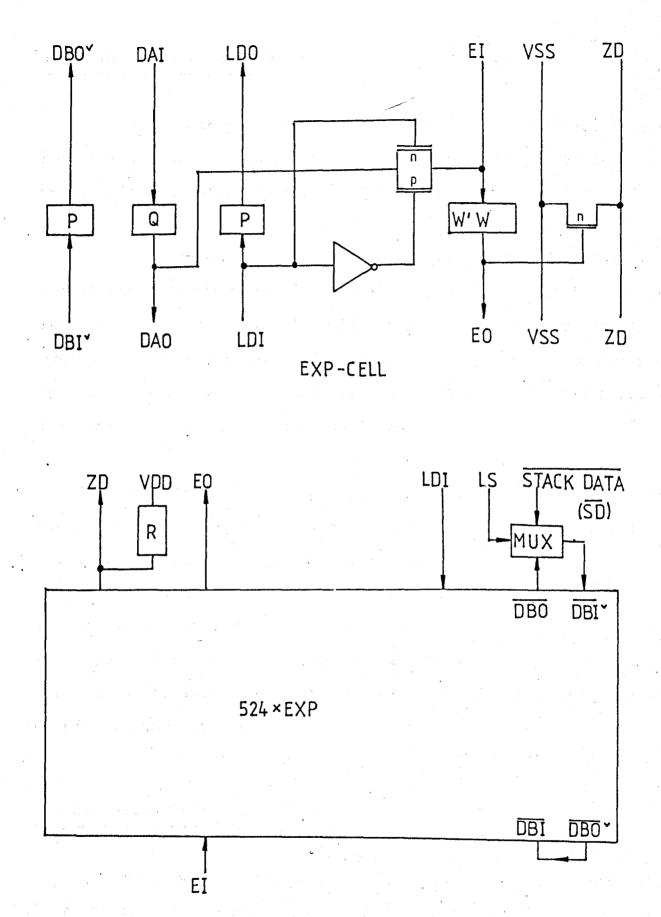

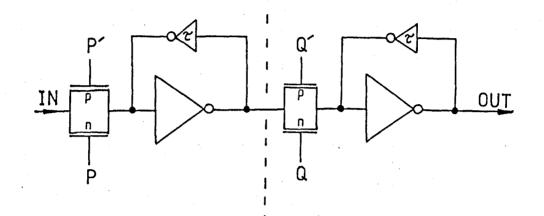

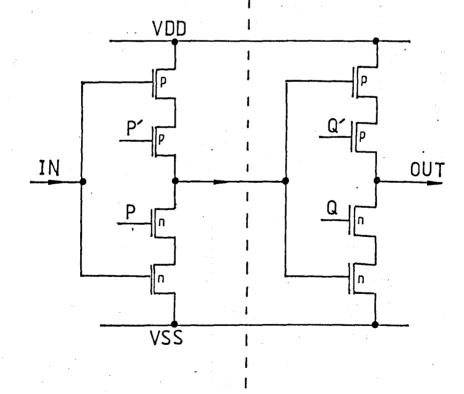

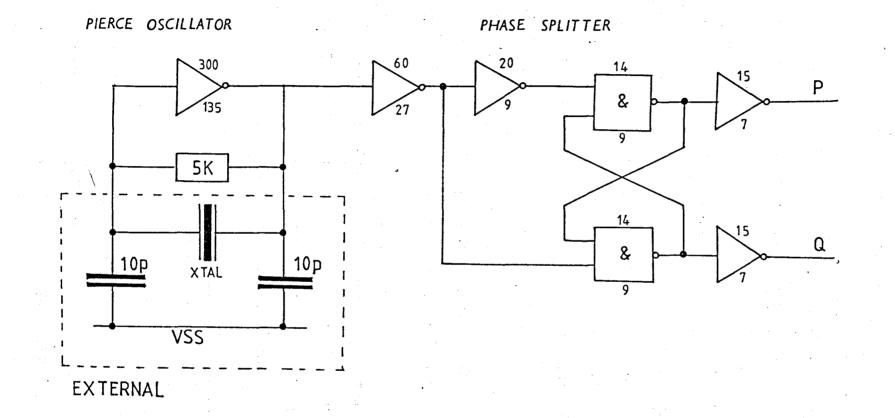

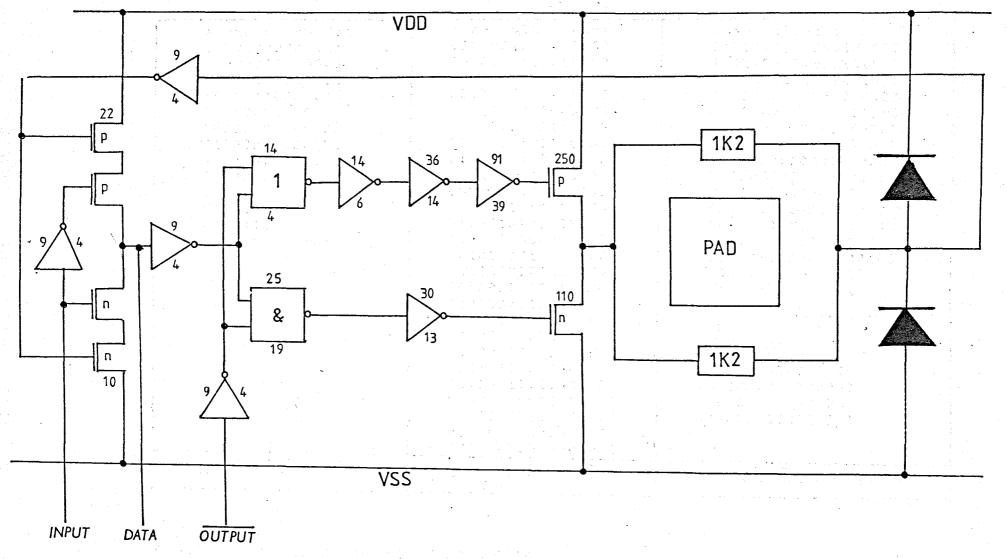

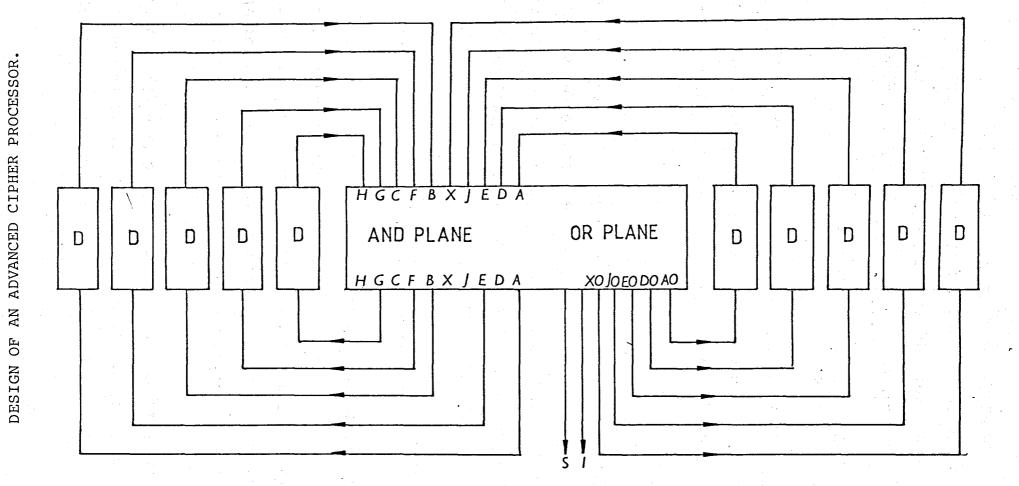

There are at present a wide variety of ways of protecting software, none of which offer 100% protection. For disc based software these include: non-standard formatting, corrupting the operating system, nibble counting, and using unique timing charcteristics of discs. However, none of these methods have proven sufficient deterrent to the skilled pirate.